Are you over 18 and want to see adult content?

More Annotations

A complete backup of drouotonline.com

Are you over 18 and want to see adult content?

A complete backup of thriftynomads.com

Are you over 18 and want to see adult content?

A complete backup of mamaslatinas.com

Are you over 18 and want to see adult content?

A complete backup of jasoncrawford.org

Are you over 18 and want to see adult content?

A complete backup of dermabalance.net

Are you over 18 and want to see adult content?

A complete backup of trinidadandtobagonews.com

Are you over 18 and want to see adult content?

Favourite Annotations

A complete backup of jee-q.tumblr.com

Are you over 18 and want to see adult content?

A complete backup of islamacademy.net

Are you over 18 and want to see adult content?

A complete backup of tradetested.co.nz

Are you over 18 and want to see adult content?

A complete backup of athleticscholarships.net

Are you over 18 and want to see adult content?

A complete backup of forewordreviews.com

Are you over 18 and want to see adult content?

A complete backup of taboo-blog.tumblr.com

Are you over 18 and want to see adult content?

Text

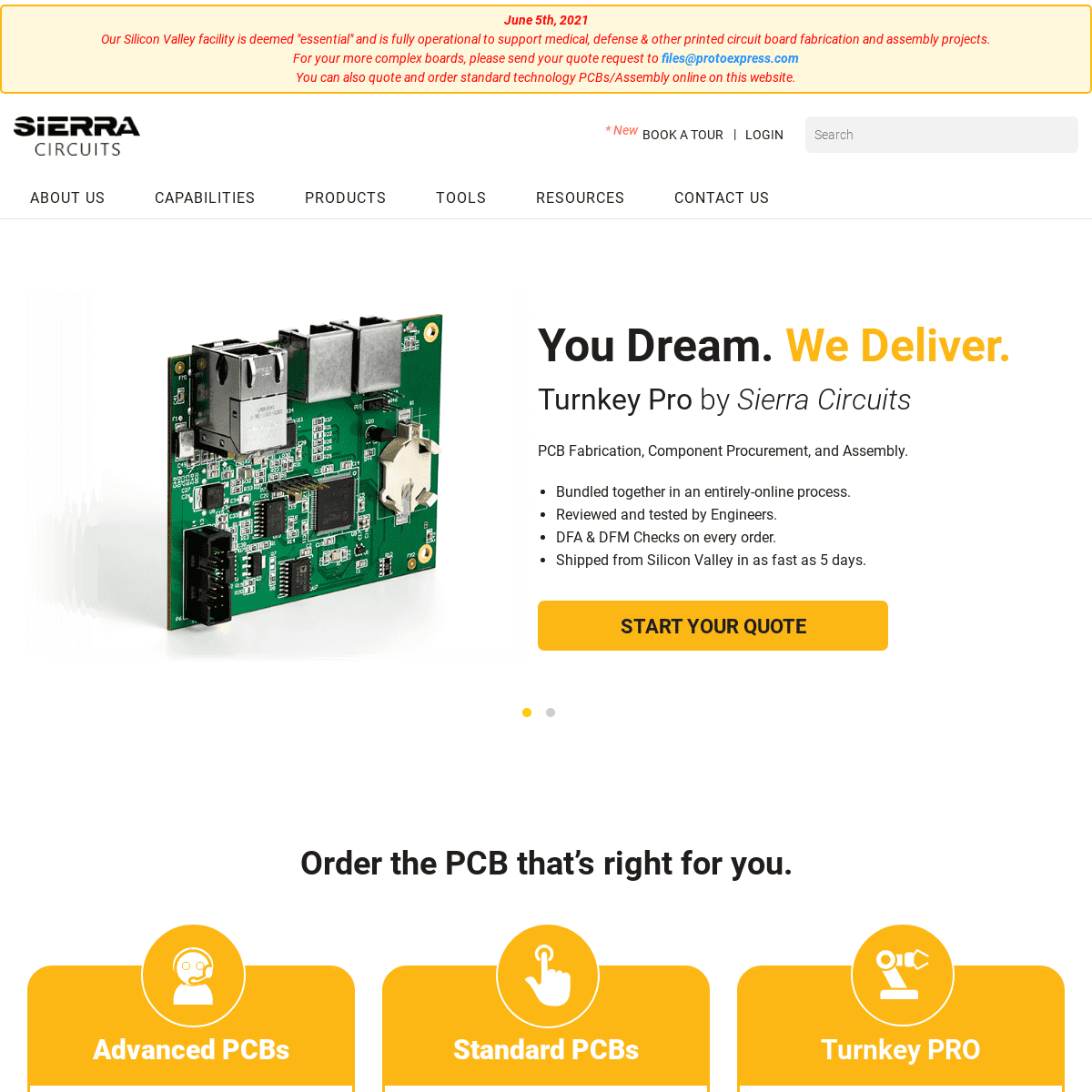

NO TOUCH PCB

Get standard 2 layer PCBs for $29 & 4 layer PCBs for $49. FR-4, 0.062SIERRA CIRCUITS

Sierra Circuits pays close attention to ensuring high-quality, controlled impedance, and impedance design. In fact, we created an impedance calculator so customers could check impedance levels before designing begins. Make sure all your single-ended and differential-pair impedance traces are manufacturable. Create customcalculations and

DESIGN RULE CHECK (DRC) FOR PCB MANUFACTURING To learn about pad design, read What is a Pad in PCB Design and Development?. Annular ring checks: To achieve acceptance for Class 2 and Class 3, follow the tables below published by Altium.The first one gives the annular ring requirements for mechanically drilled blind, buried, and through-holes on ½ oz copper:; Class 2 IPC-6012 OR IPC-A-600: WHICH STANDARD SHOULD YOU USE IPC-6012 is the specification and IPC-A-600 is the visual representation of the IPC-6012 document. They both work hand in hand. However, manufacturers like Sierra Circuits inspect their boards at their PCB assembly facility with the help of IPC-A-600. Sierra is capable of certifying to IPC-6012, IPC-6013, IPC-6015, IPC-6018, aswell as IPC-A-600.

LEARN ABOUT DESIGNING PCB VIAS AND THEIR TYPES Via-in-pad design requires filling. Dog-bone design: Separate each via from its pad with a predefined short trace covered with solder mask. Ensure there is no mask clearance for the vias under BGA. The board documentation should include a drill file with tool codes and X-Y coordinates for all holes. FREE PCB STACKUP PLANNER TOOL PCB Stackup Planner. An accurate and detailed PCB stack-up at the beginning stages of a layout reduces unnecessary iterations and helps optimize the costs by increasing manufacturability and electrical performance for a given design. This tool offers precise options for cost-optimized stack-up structures and has an integrated Impedance HOW TO REDUCE PARASITIC CAPACITANCE IN PCB LAYOUT Closely placed PCB conductors form a virtual capacitor, resulting in a parasitic capacitance effect. Parasitic capacitance or stray capacitance is the result of a virtual capacitor formed between two traces separated by a dielectric. It occurs due to the potential difference generated when the current-carrying traces run in closeproximity.

HOW FLYING PROBE TESTING WORKS FOR PCB ASSEMBLY The Flying Probe Tester in our PCB assembly facility. Flying probe testing, as the name implies uses test probes that “fly” i.e. the test probes move from test points to other test points as per instructions given by the specific software program that is written for the board under test. No custom fixture is required, so it couldalso be

PCB TRACE WIDTH, CURRENT CAPACITY AND TEMPERATURE RISE Tool calculations are based on the IPC-2152. The new IPC-2152 standard is a significant improvement over the previous IPC-2221 standard. Disclaimer: Our trace width calculator tool is exclusively designed to evaluate optimum trace width, maximum trace current, and temperature rise above the ambient required for a feasible PCB design. PCB MANUFACTURING & ASSEMBLY IN THE USA Sierra Circuits. PCB Fabrication, Component Procurement, and Assembly. Bundled together in an entirely-online process. Reviewed and tested by Engineers. DFA & DFM Checks on every order. Shipped from Silicon Valley in as fast as 5 days. Start Your Quote. You Dream. We Deliver.NO TOUCH PCB

Get standard 2 layer PCBs for $29 & 4 layer PCBs for $49. FR-4, 0.062SIERRA CIRCUITS

Sierra Circuits pays close attention to ensuring high-quality, controlled impedance, and impedance design. In fact, we created an impedance calculator so customers could check impedance levels before designing begins. Make sure all your single-ended and differential-pair impedance traces are manufacturable. Create customcalculations and

DESIGN RULE CHECK (DRC) FOR PCB MANUFACTURING To learn about pad design, read What is a Pad in PCB Design and Development?. Annular ring checks: To achieve acceptance for Class 2 and Class 3, follow the tables below published by Altium.The first one gives the annular ring requirements for mechanically drilled blind, buried, and through-holes on ½ oz copper:; Class 2 IPC-6012 OR IPC-A-600: WHICH STANDARD SHOULD YOU USE IPC-6012 is the specification and IPC-A-600 is the visual representation of the IPC-6012 document. They both work hand in hand. However, manufacturers like Sierra Circuits inspect their boards at their PCB assembly facility with the help of IPC-A-600. Sierra is capable of certifying to IPC-6012, IPC-6013, IPC-6015, IPC-6018, aswell as IPC-A-600.

LEARN ABOUT DESIGNING PCB VIAS AND THEIR TYPES Via-in-pad design requires filling. Dog-bone design: Separate each via from its pad with a predefined short trace covered with solder mask. Ensure there is no mask clearance for the vias under BGA. The board documentation should include a drill file with tool codes and X-Y coordinates for all holes. FREE PCB STACKUP PLANNER TOOL PCB Stackup Planner. An accurate and detailed PCB stack-up at the beginning stages of a layout reduces unnecessary iterations and helps optimize the costs by increasing manufacturability and electrical performance for a given design. This tool offers precise options for cost-optimized stack-up structures and has an integrated Impedance HOW TO REDUCE PARASITIC CAPACITANCE IN PCB LAYOUT Closely placed PCB conductors form a virtual capacitor, resulting in a parasitic capacitance effect. Parasitic capacitance or stray capacitance is the result of a virtual capacitor formed between two traces separated by a dielectric. It occurs due to the potential difference generated when the current-carrying traces run in closeproximity.

HOW FLYING PROBE TESTING WORKS FOR PCB ASSEMBLY The Flying Probe Tester in our PCB assembly facility. Flying probe testing, as the name implies uses test probes that “fly” i.e. the test probes move from test points to other test points as per instructions given by the specific software program that is written for the board under test. No custom fixture is required, so it couldalso be

PCB TRACE WIDTH, CURRENT CAPACITY AND TEMPERATURE RISE Tool calculations are based on the IPC-2152. The new IPC-2152 standard is a significant improvement over the previous IPC-2221 standard. Disclaimer: Our trace width calculator tool is exclusively designed to evaluate optimum trace width, maximum trace current, and temperature rise above the ambient required for a feasible PCB design.NO TOUCH PCB

Get standard 2 layer PCBs for $29 & 4 layer PCBs for $49. FR-4, 0.062SIERRA CIRCUITS

Sierra Circuits pays close attention to ensuring high-quality, controlled impedance, and impedance design. In fact, we created an impedance calculator so customers could check impedance levels before designing begins. Make sure all your single-ended and differential-pair impedance traces are manufacturable. Create customcalculations and

COPPER WRAP PLATING REQUIREMENT FOR PCB MANUFACTURING The IPC 6021B standard has included a copper wrap plating requirement for via-in-pad structures. The filled copper plating should continue around the edge of the via hole and extend onto the annular ring surrounding the via pad. The requirement enhances the reliability of the via plating and can potentially minimize failure due to cracks or THE ADVANTAGES OF METAL CORE PRINTED CIRCUIT BOARDS The Advantages of Metal Core Printed Circuit Boards. When the temperature of a PCB assembly starts rising, the owner of that board begins to sweat profusely. Clearly, they feel the heat more than the components on the board do. Jokes apart, don’t lose your cool, metal cores are here for you. 7 TIPS AND PCB DESIGN GUIDELINES FOR EMI AND EMC 1.1 Trace separation: All signals (clocks, video, audio, reset, etc.) must be separated from other traces. the general rule says that the separation between the traces should be 3W, where ‘W’ is the width of the trace. This practice helps to reduce crosstalk and HOW TO USE VIA-IN-PAD FOR PCB DESIGN AND MANUFACTURING Here the via is placed directly on the copper pad of a surface-mounted component and plated with copper (VIPPO), as opposed to a conventional via in which the signal carrying trace is routed away from the pad (dog-bone), to the via. A via-in-pad serves the function of miniaturizing the PCB form factor by reducing the space taken up bytrace

ANNULAR RING EXPLAINED BY A PCB MANUFACTURER Annular ring provides an area for connecting leads or wires to the electronic component, which serves as an anchor for the circuit. The minimum annular ring diameter will be determined by the manufacturer’s PCB assembly capabilities which can vary based on the nature of the holes and whether or not they are plated.. Constructionof an annular ring

THE BENEFITS AND CHALLENGES OF MICROELECTRONICS DESIGNS The microelectronics market is growing—fast. We’ll focus on some of the benefits and challenges of microelectronics designs. To make the most of the microelectronics space, companies must ensure they’re accommodating microelectronics’ limitations andadvantages.

8 COMMON ERRORS IN SURFACE MOUNT TECHNOLOGY Surface mount technology is not a zero-defect soldering process.In this article, we will look into simple defects in surface mount technology (SMT) that cause your PCB to fail and try to work out how to avoid them. Reducing such defects is the key to providing efficient PCB assembly services.. We will cover the following topics through the course of this article: PCB LINE SPACING FOR CREEPAGE AND CLEARANCE The minimum line spacing between PCB components and other traces is the distance required to withstand a given voltage. It is defined in terms of creepage and clearance distances. Factors such as voltage, application, and the type of PCB assembly play a key role in determining the minimum PCB line spacing requirements.SIERRA CIRCUITS

Sierra Circuits. PCB Fabrication, Component Procurement, and Assembly. Bundled together in an entirely-online process. Reviewed and tested by Engineers. DFA & DFM Checks on every order. Shipped from Silicon Valley in as fast as 5 days. Start Your Quote. You Dream. We Deliver. DESIGN RULE CHECK (DRC) FOR PCB MANUFACTURING To learn about pad design, read What is a Pad in PCB Design and Development?. Annular ring checks: To achieve acceptance for Class 2 and Class 3, follow the tables below published by Altium.The first one gives the annular ring requirements for mechanically drilled blind, buried, and through-holes on ½ oz copper:; Class 2 LEARN ABOUT DESIGNING PCB VIAS AND THEIR TYPES Via-in-pad design requires filling. Dog-bone design: Separate each via from its pad with a predefined short trace covered with solder mask. Ensure there is no mask clearance for the vias under BGA. The board documentation should include a drill file with tool codes and X-Y coordinates for all holes. IPC-6012 OR IPC-A-600: WHICH STANDARD SHOULD YOU USE IPC-6012 is the specification and IPC-A-600 is the visual representation of the IPC-6012 document. They both work hand in hand. However, manufacturers like Sierra Circuits inspect their boards at their PCB assembly facility with the help of IPC-A-600. Sierra is capable of certifying to IPC-6012, IPC-6013, IPC-6015, IPC-6018, aswell as IPC-A-600.

COPPER WRAP PLATING REQUIREMENT FOR PCB MANUFACTURING The IPC 6021B standard has included a copper wrap plating requirement for via-in-pad structures. The filled copper plating should continue around the edge of the via hole and extend onto the annular ring surrounding the via pad. The requirement enhances the reliability of the via plating and can potentially minimize failure due to cracks or MILITARY-GRADE PCB DESIGN RULES AND CONSIDERATIONS A military-grade printed circuit board must be designed from scratch as a military spec or IPC 6012 class 3/A. The design, layout, material selection, and fabrication processes should follow the stringent standards. These PCBs are fabricated by qualified manufacturers who are capable of working with tight parameters and tolerances. ENEPIG PCB – SIERRA CIRCUITS ENEPIG . ENEPIG is a type of surface finish done on copper layer to protect it from oxidation and corrosion in printed circuit boards. This surface finish improves the solderability of HOW TO REDUCE PARASITIC CAPACITANCE IN PCB LAYOUT Closely placed PCB conductors form a virtual capacitor, resulting in a parasitic capacitance effect. Parasitic capacitance or stray capacitance is the result of a virtual capacitor formed between two traces separated by a dielectric. It occurs due to the potential difference generated when the current-carrying traces run in closeproximity.

PCB SUBSTRATES: KNOWING YOUR PCB DIELECTRIC MATERIALSSEE MORE ONPROTOEXPRESS.COM

PCB TRACE WIDTH, CURRENT CAPACITY AND TEMPERATURE RISE Tool calculations are based on the IPC-2152. The new IPC-2152 standard is a significant improvement over the previous IPC-2221 standard. Disclaimer: Our trace width calculator tool is exclusively designed to evaluate optimum trace width, maximum trace current, and temperature rise above the ambient required for a feasible PCB design.SIERRA CIRCUITS

Sierra Circuits. PCB Fabrication, Component Procurement, and Assembly. Bundled together in an entirely-online process. Reviewed and tested by Engineers. DFA & DFM Checks on every order. Shipped from Silicon Valley in as fast as 5 days. Start Your Quote. You Dream. We Deliver. DESIGN RULE CHECK (DRC) FOR PCB MANUFACTURING To learn about pad design, read What is a Pad in PCB Design and Development?. Annular ring checks: To achieve acceptance for Class 2 and Class 3, follow the tables below published by Altium.The first one gives the annular ring requirements for mechanically drilled blind, buried, and through-holes on ½ oz copper:; Class 2 LEARN ABOUT DESIGNING PCB VIAS AND THEIR TYPES Via-in-pad design requires filling. Dog-bone design: Separate each via from its pad with a predefined short trace covered with solder mask. Ensure there is no mask clearance for the vias under BGA. The board documentation should include a drill file with tool codes and X-Y coordinates for all holes. IPC-6012 OR IPC-A-600: WHICH STANDARD SHOULD YOU USE IPC-6012 is the specification and IPC-A-600 is the visual representation of the IPC-6012 document. They both work hand in hand. However, manufacturers like Sierra Circuits inspect their boards at their PCB assembly facility with the help of IPC-A-600. Sierra is capable of certifying to IPC-6012, IPC-6013, IPC-6015, IPC-6018, aswell as IPC-A-600.

COPPER WRAP PLATING REQUIREMENT FOR PCB MANUFACTURING The IPC 6021B standard has included a copper wrap plating requirement for via-in-pad structures. The filled copper plating should continue around the edge of the via hole and extend onto the annular ring surrounding the via pad. The requirement enhances the reliability of the via plating and can potentially minimize failure due to cracks or MILITARY-GRADE PCB DESIGN RULES AND CONSIDERATIONS A military-grade printed circuit board must be designed from scratch as a military spec or IPC 6012 class 3/A. The design, layout, material selection, and fabrication processes should follow the stringent standards. These PCBs are fabricated by qualified manufacturers who are capable of working with tight parameters and tolerances. ENEPIG PCB – SIERRA CIRCUITS ENEPIG . ENEPIG is a type of surface finish done on copper layer to protect it from oxidation and corrosion in printed circuit boards. This surface finish improves the solderability of HOW TO REDUCE PARASITIC CAPACITANCE IN PCB LAYOUT Closely placed PCB conductors form a virtual capacitor, resulting in a parasitic capacitance effect. Parasitic capacitance or stray capacitance is the result of a virtual capacitor formed between two traces separated by a dielectric. It occurs due to the potential difference generated when the current-carrying traces run in closeproximity.

PCB SUBSTRATES: KNOWING YOUR PCB DIELECTRIC MATERIALSSEE MORE ONPROTOEXPRESS.COM

PCB TRACE WIDTH, CURRENT CAPACITY AND TEMPERATURE RISE Tool calculations are based on the IPC-2152. The new IPC-2152 standard is a significant improvement over the previous IPC-2221 standard. Disclaimer: Our trace width calculator tool is exclusively designed to evaluate optimum trace width, maximum trace current, and temperature rise above the ambient required for a feasible PCB design.SIERRA CIRCUITS

Sierra Circuits pays close attention to ensuring high-quality, controlled impedance, and impedance design. In fact, we created an impedance calculator so customers could check impedance levels before designing begins. Make sure all your single-ended and differential-pair impedance traces are manufacturable. Create customcalculations and

THE LIDAR MARKET

The global LiDAR market is expected to witness a CAGR of 14.1% during the forecast period to reach revenue of $2.91 billion by 2025.PCB DRILLING

A rule is a rule even for a hole. Plated through-hole (PTH): Finished hole size (minimum) = 4 mils. Annular ring size (minimum) = 3 mils. Drill diameter tolerances must be specified on the drill chart. Sierra Circuits prefers a drill diameter tolerance of +/- 0.003” for PTH and NPTH drills. The accuracy of the hole location is compromised ENEPIG PCB – SIERRA CIRCUITS ENEPIG . ENEPIG is a type of surface finish done on copper layer to protect it from oxidation and corrosion in printed circuit boards. This surface finish improves the solderability of WHAT IS SOLDER MASK LAYER? Solder mask is a thin layer of polymer that is put on a circuit board to protect the copper from oxidation and shorts during operation. It also protects the PCB from environmental influences such as dust and several other contaminants that may lead to shorts in the long run. Panels that are coated with solder mask. PCB LINE SPACING FOR CREEPAGE AND CLEARANCE The minimum line spacing between PCB components and other traces is the distance required to withstand a given voltage. It is defined in terms of creepage and clearance distances. Factors such as voltage, application, and the type of PCB assembly play a key role in determining the minimum PCB line spacing requirements. THE BENEFITS AND CHALLENGES OF MICROELECTRONICS DESIGNS The microelectronics market is growing—fast. We’ll focus on some of the benefits and challenges of microelectronics designs. To make the most of the microelectronics space, companies must ensure they’re accommodating microelectronics’ limitations andadvantages.

PCB STACKUP PLANNER

PCB Stackup Planner. An accurate and detailed PCB stack-up at the beginning stages of a layout reduces unnecessary iterations and helps optimize the costs by increasing manufacturability and electrical performance for a given design. This tool offers precise options for cost-optimized stack-up structures and has an integrated Impedance HOW TO USE VIA-IN-PAD FOR PCB DESIGN AND MANUFACTURING Here the via is placed directly on the copper pad of a surface-mounted component and plated with copper (VIPPO), as opposed to a conventional via in which the signal carrying trace is routed away from the pad (dog-bone), to the via. A via-in-pad serves the function of miniaturizing the PCB form factor by reducing the space taken up bytrace

7 TIPS AND PCB DESIGN GUIDELINES FOR EMI AND EMC 1.1 Trace separation: All signals (clocks, video, audio, reset, etc.) must be separated from other traces. the general rule says that the separation between the traces should be 3W, where ‘W’ is the width of the trace. This practice helps to reduce crosstalk andSIERRA CIRCUITS

Sierra Circuits. PCB Fabrication, Component Procurement, and Assembly. Bundled together in an entirely-online process. Reviewed and tested by Engineers. DFA & DFM Checks on every order. Shipped from Silicon Valley in as fast as 5 days. Start Your Quote. You Dream. We Deliver.DESIGNING PCB VIAS

Check for minimum clearance of traces and vias from the routed/scored edges. Check the position of vias for BGA packages. Via-in-pad design requires filling. Dog-bone design: Separate each via from its pad with a predefined short trace covered with solder mask. IPC-6012 OR IPC-A-600: WHICH STANDARD SHOULD YOU USE IPC-6012 is the specification and IPC-A-600 is the visual representation of the IPC-6012 document. They both work hand in hand. However, manufacturers like Sierra Circuits inspect their boards at their PCB assembly facility with the help of IPC-A-600. Sierra is capable of certifying to IPC-6012, IPC-6013, IPC-6015, IPC-6018, aswell as IPC-A-600.

MILITARY-GRADE PCB DESIGN RULES AND CONSIDERATIONS A military-grade printed circuit board must be designed from scratch as a military spec or IPC 6012 class 3/A. The design, layout, material selection, and fabrication processes should follow the stringent standards. These PCBs are fabricated by qualified manufacturers who are capable of working with tight parameters and tolerances. ENEPIG PCB – SIERRA CIRCUITS ENEPIG . ENEPIG is a type of surface finish done on copper layer to protect it from oxidation and corrosion in printed circuit boards. This surface finish improves the solderability ofANNULAR RING

Annular breakouts occur when the drilled via is not fully encircled by the pad. This can happen when the lamination process causes the PCB to shift and move away from where parts (pads, traces, etc.) should be. This is a problem when drilling, as annular breakouts can occur. Breakouts of 90 to 180 degrees can occur. A 90-degree annularbreakout.

ANNULAR RING EXPLAINED BY A PCB MANUFACTURER Annular Ring. 2:48. Annular ring provides an area for connecting leads or wires to the electronic component, which serves as an anchor for the circuit. The minimum annular ring diameter will be determined by the manufacturer’s PCB assembly capabilities which can vary based on the nature of the holes and whether or not they are plated. IPC CLASS 2 VS CLASS 3: THE DIFFERENT DESIGN RULESSEE MORE ONPROTOEXPRESS.COM

PCB LINE SPACING FOR CREEPAGE AND CLEARANCE The minimum line spacing between PCB components and other traces is the distance required to withstand a given voltage. It is defined in terms of creepage and clearance distances. Factors such as voltage, application, and the type of PCB assembly play a key role in determining the minimum PCB line spacing requirements. PCB TRACE WIDTH, CURRENT CAPACITY AND TEMPERATURE RISE Tool calculations are based on the IPC-2152. The new IPC-2152 standard is a significant improvement over the previous IPC-2221 standard. Disclaimer: Our trace width calculator tool is exclusively designed to evaluate optimum trace width, maximum trace current, and temperature rise above the ambient required for a feasible PCB design.SIERRA CIRCUITS

Sierra Circuits. PCB Fabrication, Component Procurement, and Assembly. Bundled together in an entirely-online process. Reviewed and tested by Engineers. DFA & DFM Checks on every order. Shipped from Silicon Valley in as fast as 5 days. Start Your Quote. You Dream. We Deliver.DESIGNING PCB VIAS

Check for minimum clearance of traces and vias from the routed/scored edges. Check the position of vias for BGA packages. Via-in-pad design requires filling. Dog-bone design: Separate each via from its pad with a predefined short trace covered with solder mask. IPC-6012 OR IPC-A-600: WHICH STANDARD SHOULD YOU USE IPC-6012 is the specification and IPC-A-600 is the visual representation of the IPC-6012 document. They both work hand in hand. However, manufacturers like Sierra Circuits inspect their boards at their PCB assembly facility with the help of IPC-A-600. Sierra is capable of certifying to IPC-6012, IPC-6013, IPC-6015, IPC-6018, aswell as IPC-A-600.

MILITARY-GRADE PCB DESIGN RULES AND CONSIDERATIONS A military-grade printed circuit board must be designed from scratch as a military spec or IPC 6012 class 3/A. The design, layout, material selection, and fabrication processes should follow the stringent standards. These PCBs are fabricated by qualified manufacturers who are capable of working with tight parameters and tolerances. ENEPIG PCB – SIERRA CIRCUITS ENEPIG . ENEPIG is a type of surface finish done on copper layer to protect it from oxidation and corrosion in printed circuit boards. This surface finish improves the solderability ofANNULAR RING

Annular breakouts occur when the drilled via is not fully encircled by the pad. This can happen when the lamination process causes the PCB to shift and move away from where parts (pads, traces, etc.) should be. This is a problem when drilling, as annular breakouts can occur. Breakouts of 90 to 180 degrees can occur. A 90-degree annularbreakout.

ANNULAR RING EXPLAINED BY A PCB MANUFACTURER Annular Ring. 2:48. Annular ring provides an area for connecting leads or wires to the electronic component, which serves as an anchor for the circuit. The minimum annular ring diameter will be determined by the manufacturer’s PCB assembly capabilities which can vary based on the nature of the holes and whether or not they are plated. IPC CLASS 2 VS CLASS 3: THE DIFFERENT DESIGN RULESSEE MORE ONPROTOEXPRESS.COM

PCB LINE SPACING FOR CREEPAGE AND CLEARANCE The minimum line spacing between PCB components and other traces is the distance required to withstand a given voltage. It is defined in terms of creepage and clearance distances. Factors such as voltage, application, and the type of PCB assembly play a key role in determining the minimum PCB line spacing requirements. PCB TRACE WIDTH, CURRENT CAPACITY AND TEMPERATURE RISE Tool calculations are based on the IPC-2152. The new IPC-2152 standard is a significant improvement over the previous IPC-2221 standard. Disclaimer: Our trace width calculator tool is exclusively designed to evaluate optimum trace width, maximum trace current, and temperature rise above the ambient required for a feasible PCB design.NO TOUCH PCB

Get standard 2 layer PCBs for $29 & 4 layer PCBs for $49. FR-4, 0.062DESIGNING PCB VIAS

Check for minimum clearance of traces and vias from the routed/scored edges. Check the position of vias for BGA packages. Via-in-pad design requires filling. Dog-bone design: Separate each via from its pad with a predefined short trace covered with solder mask.PCB DRILLING

A rule is a rule even for a hole. Plated through-hole (PTH): Finished hole size (minimum) = 4 mils. Annular ring size (minimum) = 3 mils. Drill diameter tolerances must be specified on the drill chart. Sierra Circuits prefers a drill diameter tolerance of +/- 0.003” for PTH and NPTH drills. The accuracy of the hole location is compromised CONTACT US – SIERRA CIRCUITS Silicon Valley Campus (HQ) Sierra Circuits, Inc. 1108 West Evelyn Avenue Sunnyvale, CA 94086 Toll free: (800) 763-7503 Phone: (408) 735-7137 Fax: (408) 735-1408PCB STACKUP PLANNER

PCB Stackup Planner. An accurate and detailed PCB stack-up at the beginning stages of a layout reduces unnecessary iterations and helps optimize the costs by increasing manufacturability and electrical performance for a given design. This tool offers precise options for cost-optimized stack-up structures and has an integrated Impedance 7 TIPS AND PCB DESIGN GUIDELINES FOR EMI AND EMC 1.1 Trace separation: All signals (clocks, video, audio, reset, etc.) must be separated from other traces. the general rule says that the separation between the traces should be 3W, where ‘W’ is the width of the trace. This practice helps to reduce crosstalk and HOW TO BREAKOUT A BGA: TWO EXAMPLES OF A .4MM BGA How to breakout a .4mm BGA: Example #2. This is a .4mm BGA pitch on a 6×6 matrix. It has 4-5 mil trace/space, with 4-mil lasers and 8-mil pads. The routing strategy includes stacked and staggered vias. This PCB has 4-mil vias. The material thickness between layers 1 – 2 should be 4 mils, max. 8 COMMON ERRORS IN SURFACE MOUNT TECHNOLOGY Surface mount technology is not a zero-defect soldering process.In this article, we will look into simple defects in surface mount technology (SMT) that cause your PCB to fail and try to work out how to avoid them. Reducing such defects is the key to providing efficient PCB assembly services.. We will cover the following topics through the course of this article: HOW TO CHOOSE HDI PCB MATERIALS An HDI PCB is characterized by its high density of components and routing interconnections. An HDI design is by its very nature a high-performance design. It has fine lines and spaces (≤100µm),small vias (

Details

Copyright © 2024 ArchiveBay.com. All rights reserved. Terms of Use | Privacy Policy | DMCA | 2021 | Feedback | Advertising | RSS 2.0