Are you over 18 and want to see adult content?

More Annotations

A complete backup of https://cerave.co.th

Are you over 18 and want to see adult content?

A complete backup of https://popbrixton.org

Are you over 18 and want to see adult content?

A complete backup of https://alexcymusrofic.cf

Are you over 18 and want to see adult content?

A complete backup of https://staglinfamily.com

Are you over 18 and want to see adult content?

A complete backup of https://simpleeverydaymom.com

Are you over 18 and want to see adult content?

A complete backup of https://athleticmuscle.net

Are you over 18 and want to see adult content?

A complete backup of https://zoover.nl

Are you over 18 and want to see adult content?

A complete backup of https://psfk.com

Are you over 18 and want to see adult content?

A complete backup of https://goldengoosesaleus.com

Are you over 18 and want to see adult content?

A complete backup of https://sirlinksalot.net

Are you over 18 and want to see adult content?

A complete backup of https://mandalayogaspa.com

Are you over 18 and want to see adult content?

Favourite Annotations

A complete backup of https://findingsanityinourcrazylife.com

Are you over 18 and want to see adult content?

A complete backup of https://flexperto.com

Are you over 18 and want to see adult content?

A complete backup of https://kidneypatientguide.org.uk

Are you over 18 and want to see adult content?

A complete backup of https://bryandeakin.com

Are you over 18 and want to see adult content?

A complete backup of https://orderofmalta.int

Are you over 18 and want to see adult content?

A complete backup of https://maybomhangphu.com

Are you over 18 and want to see adult content?

A complete backup of https://shufunotomo.co.jp

Are you over 18 and want to see adult content?

A complete backup of https://reincubate.com

Are you over 18 and want to see adult content?

A complete backup of https://openkey.co

Are you over 18 and want to see adult content?

A complete backup of https://mamacommunity.de

Are you over 18 and want to see adult content?

A complete backup of https://gramshark.com

Are you over 18 and want to see adult content?

A complete backup of https://korastar.us

Are you over 18 and want to see adult content?

Text

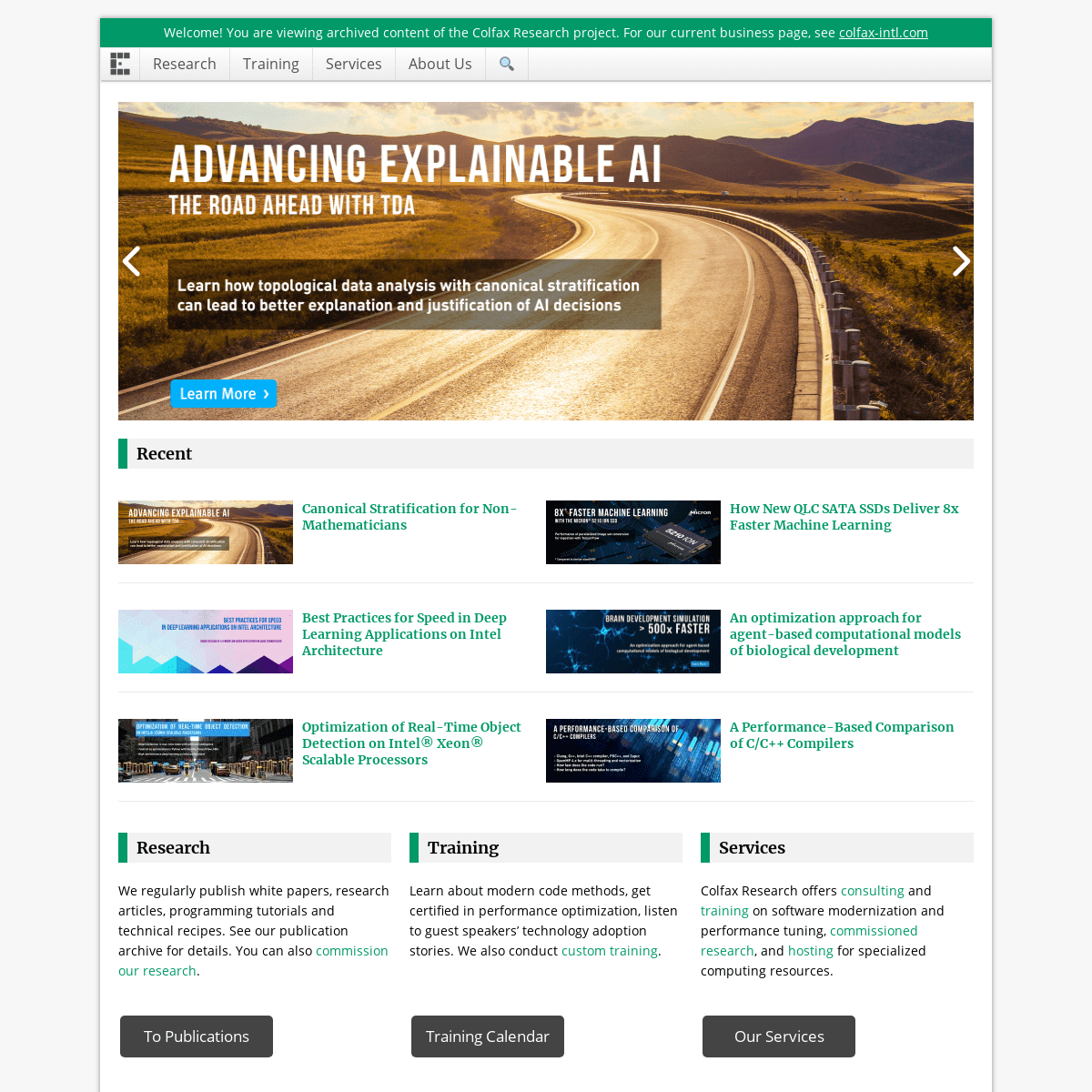

COLFAX RESEARCH

Best Practices for Speed in Deep Learning Applications on Intel Architecture. An optimization approach for agent-based computational models of biological development. Optimization of Real-Time Object Detection on Intel® Xeon® Scalable Processors. A Performance-Based Comparison of C/C++ Compilers. TRAINING | COLFAX RESEARCH As the leading provider of code modernization and optimization training, Colfax now offers a hands-on workshop (part of the HOW series) on the best practices for performance optimization for Intel® Xeon Phi processor family x200 (formerly Knights Landing). In this 2-hour webinar we will highlight the new processor features andperform hands-on

A PERFORMANCE-BASED COMPARISON OF C/C++ COMPILERS OPTIMIZATION OF REAL-TIME OBJECT DETECTION ON INTEL® XEON1. REAL-TIME OBJECT DETECTION2. TENSORFLOW AND MKL3. OPTIMIZATION OF CNN3.1. YOLOSEE MORE ON COLFAXRESEARCH.COM AN OPTIMIZATION APPROACH FOR AGENT-BASED COMPUTATIONAL a Software Performance Optimization Group, Imperial College London, London, United Kingdom b CERN Openlab, IT Department, CERN, Switzerland c Intel Corporation, USA d Colfax International, USA e Interdisciplinary Computing and Complex BioSystems Research Group, School of Computing, Newcastle University, Newcastle upon Tyne, United Kingdom f Institute of Neuroscience, Newcastle University MODERN CODE FOR INTEL XEON PHI PROCESSORS This series of 45-minute webinars was presented by Colfax International in collaboration with Intel in 2016. Part 1 | Part 2 | Part 3 1. Strategies for Multi-Threading on Intel Xeon Phi Proce HPLINPACK BENCHMARK ON INTEL XEON PHI PROCESSOR FAMILYSECTION 1. HPLINPACK BENCHMARKALGORITHMHPL CONFIGURATION FILESECTION 2. SYSTEM CONFIGURATIONSEE MORE ON COLFAXRESEARCH.COM MC² 003: PLASMA SIMULATION WITH PARTICLE-IN-CELL CODE CFHall is a plasma simulation code based on a particle-in-cell method. It uses the finite difference method on a rectangular mesh for Maxwell equations, and couples it to superparticle traversal the mesh in a self-consistent approach. The uniqueness of CFHall lies in the use of the Locally Recursive non-Locally Asynchronous (LRnLA) algorithms. A SURVEY AND BENCHMARKS OF INTEL® XEON® GOLD AND PLATINUM1. WHICH XEON IS RIGHT FOR YOU?2. CPU COMPARISON FOR DIFFERENT WORKLOADS2.4. BANDWIDTH-LIMITED3. PROCESSOR CHOICE RECOMMENDATIONSSEE MORE ONCOLFAXRESEARCH.COM

GUIDE TO AUTOMATIC VECTORIZATION WITH INTEL AVX-5121. VECTOR INSTRUCTIONS2. STRUCTURE AND FUNCTIONALITY OF AVX-5122.1. SUBSETS2.2. AVX512-FSEE MORE ON COLFAXRESEARCH.COMCOLFAX RESEARCH

Best Practices for Speed in Deep Learning Applications on Intel Architecture. An optimization approach for agent-based computational models of biological development. Optimization of Real-Time Object Detection on Intel® Xeon® Scalable Processors. A Performance-Based Comparison of C/C++ Compilers. TRAINING | COLFAX RESEARCH As the leading provider of code modernization and optimization training, Colfax now offers a hands-on workshop (part of the HOW series) on the best practices for performance optimization for Intel® Xeon Phi processor family x200 (formerly Knights Landing). In this 2-hour webinar we will highlight the new processor features andperform hands-on

A PERFORMANCE-BASED COMPARISON OF C/C++ COMPILERS OPTIMIZATION OF REAL-TIME OBJECT DETECTION ON INTEL® XEON1. REAL-TIME OBJECT DETECTION2. TENSORFLOW AND MKL3. OPTIMIZATION OF CNN3.1. YOLOSEE MORE ON COLFAXRESEARCH.COM AN OPTIMIZATION APPROACH FOR AGENT-BASED COMPUTATIONAL a Software Performance Optimization Group, Imperial College London, London, United Kingdom b CERN Openlab, IT Department, CERN, Switzerland c Intel Corporation, USA d Colfax International, USA e Interdisciplinary Computing and Complex BioSystems Research Group, School of Computing, Newcastle University, Newcastle upon Tyne, United Kingdom f Institute of Neuroscience, Newcastle University MODERN CODE FOR INTEL XEON PHI PROCESSORS This series of 45-minute webinars was presented by Colfax International in collaboration with Intel in 2016. Part 1 | Part 2 | Part 3 1. Strategies for Multi-Threading on Intel Xeon Phi Proce HPLINPACK BENCHMARK ON INTEL XEON PHI PROCESSOR FAMILYSECTION 1. HPLINPACK BENCHMARKALGORITHMHPL CONFIGURATION FILESECTION 2. SYSTEM CONFIGURATIONSEE MORE ON COLFAXRESEARCH.COM MC² 003: PLASMA SIMULATION WITH PARTICLE-IN-CELL CODE CFHall is a plasma simulation code based on a particle-in-cell method. It uses the finite difference method on a rectangular mesh for Maxwell equations, and couples it to superparticle traversal the mesh in a self-consistent approach. The uniqueness of CFHall lies in the use of the Locally Recursive non-Locally Asynchronous (LRnLA) algorithms. A SURVEY AND BENCHMARKS OF INTEL® XEON® GOLD AND PLATINUM1. WHICH XEON IS RIGHT FOR YOU?2. CPU COMPARISON FOR DIFFERENT WORKLOADS2.4. BANDWIDTH-LIMITED3. PROCESSOR CHOICE RECOMMENDATIONSSEE MORE ONCOLFAXRESEARCH.COM

GUIDE TO AUTOMATIC VECTORIZATION WITH INTEL AVX-5121. VECTOR INSTRUCTIONS2. STRUCTURE AND FUNCTIONALITY OF AVX-5122.1. SUBSETS2.2. AVX512-FSEE MORE ON COLFAXRESEARCH.COM RESEARCH PUBLICATIONS We regularly publish white papers and research publications on HPC-related technology and methods. Explore our knowledge base in this catalog of categories or visit the Archive (chronological order HOSTING | COLFAX RESEARCH Yes, we offer hosting for computing resources. No, we are not your regular cloud hosting provider. What we offer is designed specifically for the high-performance computing industry. We will build, MODERN CODE FOR INTEL XEON PHI PROCESSORS This series of 45-minute webinars was presented by Colfax International in collaboration with Intel in 2016. Part 1 | Part 2 | Part 3 1. Strategies for Multi-Threading on Intel Xeon Phi Proce HOW NEW QLC SATA SSDS DELIVER 8X FASTER MACHINE LEARNING Table 1: System Configuration. 4. Test Workload: TFRecord. TFRecord is the standard format for TensorFlow. It is used to store large amounts of data (for example, a collection of images) in a single TFRecord file, which can be read from storage faster than individual files and loaded into TensorFlow in batches for training. AN OPTIMIZATION APPROACH FOR AGENT-BASED COMPUTATIONAL a Software Performance Optimization Group, Imperial College London, London, United Kingdom b CERN Openlab, IT Department, CERN, Switzerland c Intel Corporation, USA d Colfax International, USA e Interdisciplinary Computing and Complex BioSystems Research Group, School of Computing, Newcastle University, Newcastle upon Tyne, United Kingdom f Institute of Neuroscience, Newcastle University MC² 004: SIGNAL PROCESSING IN A PHYSICS The work of Prof. Jeffrey Dunham connects real-world phenomena to data collection to computing in a very pure experiment. He has built a tabletop-scale chaotic pendulum equipped with a high-precision rotary encoder. The pendulum produces hundreds of gigabytes of data per day. This data reveals the strange attractor of the pendulum, which is a INTRODUCTION TO INTEL DAAL, PART 1: POLYNOMIAL REGRESSION This is the part 1 of 3 of an introductory series of publications on the Intel Data Analytics Acceleration Library (DAAL). DAAL is a data analytics library optimized for modern highly parallel computer architectures such as Intel Xeon and Intel Xeon Phi processors. CAPABILITIES OF INTEL® AVX-512 IN INTEL® XEON® SCALABLE Later, in 2017, AVX-512 was used in Intel® Xeon® processor Scalable family (formerly Skylake). The most notable new feature of AVX-512 compared to AVX/AVX2 is the 512-bit vector register width, which is twice the size of the AVX/AVX2 registers. However, AVX-512 is more than just a promotion of the vector register width from 256 to 512bits.

MEET US AT SC16

Reddit. If you are going to the SC16 conference, visit Colfax: At the Intel HPC Developer Conference (free pre-SC16 event) When: on Sunday, November 13, 2016, at 9:45 am – 10:35 am. Where: Sheraton Salt Lake City Hotel. Event: Technical session “Optimizing Machine Learning Workloads on Intel Platforms”. On the SC’16 exhibition floor. MCDRAM AS HIGH-BANDWIDTH MEMORY (HBM) IN KNIGHTS LANDING The Flat mode uses the entirety of HBM as addressable memory, whereas Cache mode uses the entirety of HBM as cache. With Hybrid mode, a portion of the HBM is used as addressable memory and the rest is used as cache.Addressable memory may be utilized by the user for explicit allocation of objects, while HBM as cache is not visible in the operating system (OS) and operates “behind the scenesCOLFAX RESEARCH

Best Practices for Speed in Deep Learning Applications on Intel Architecture. An optimization approach for agent-based computational models of biological development. Optimization of Real-Time Object Detection on Intel® Xeon® Scalable Processors. A Performance-Based Comparison of C/C++ Compilers. TRAINING | COLFAX RESEARCH As the leading provider of code modernization and optimization training, Colfax now offers a hands-on workshop (part of the HOW series) on the best practices for performance optimization for Intel® Xeon Phi processor family x200 (formerly Knights Landing). In this 2-hour webinar we will highlight the new processor features andperform hands-on

A PERFORMANCE-BASED COMPARISON OF C/C++ COMPILERS MODERN CODE FOR INTEL XEON PHI PROCESSORS This series of 45-minute webinars was presented by Colfax International in collaboration with Intel in 2016. Part 1 | Part 2 | Part 3 1. Strategies for Multi-Threading on Intel Xeon Phi Proce OPTIMIZATION OF REAL-TIME OBJECT DETECTION ON INTEL® XEON1. REAL-TIME OBJECT DETECTION2. TENSORFLOW AND MKL3. OPTIMIZATION OF CNN3.1. YOLOSEE MORE ON COLFAXRESEARCH.COM HOW NEW QLC SATA SSDS DELIVER 8X FASTER MACHINE LEARNING Table 1: System Configuration. 4. Test Workload: TFRecord. TFRecord is the standard format for TensorFlow. It is used to store large amounts of data (for example, a collection of images) in a single TFRecord file, which can be read from storage faster than individual files and loaded into TensorFlow in batches for training. HPLINPACK BENCHMARK ON INTEL XEON PHI PROCESSOR FAMILYSECTION 1. HPLINPACK BENCHMARKALGORITHMHPL CONFIGURATION FILESECTION 2. SYSTEM CONFIGURATIONSEE MORE ON COLFAXRESEARCH.COM MC² 003: PLASMA SIMULATION WITH PARTICLE-IN-CELL CODE CFHall is a plasma simulation code based on a particle-in-cell method. It uses the finite difference method on a rectangular mesh for Maxwell equations, and couples it to superparticle traversal the mesh in a self-consistent approach. The uniqueness of CFHall lies in the use of the Locally Recursive non-Locally Asynchronous (LRnLA) algorithms. A SURVEY AND BENCHMARKS OF INTEL® XEON® GOLD AND PLATINUM1. WHICH XEON IS RIGHT FOR YOU?2. CPU COMPARISON FOR DIFFERENT WORKLOADS2.4. BANDWIDTH-LIMITED3. PROCESSOR CHOICE RECOMMENDATIONSSEE MORE ONCOLFAXRESEARCH.COM

GUIDE TO AUTOMATIC VECTORIZATION WITH INTEL AVX-5121. VECTOR INSTRUCTIONS2. STRUCTURE AND FUNCTIONALITY OF AVX-5122.1. SUBSETS2.2. AVX512-FSEE MORE ON COLFAXRESEARCH.COMCOLFAX RESEARCH

Best Practices for Speed in Deep Learning Applications on Intel Architecture. An optimization approach for agent-based computational models of biological development. Optimization of Real-Time Object Detection on Intel® Xeon® Scalable Processors. A Performance-Based Comparison of C/C++ Compilers. TRAINING | COLFAX RESEARCH As the leading provider of code modernization and optimization training, Colfax now offers a hands-on workshop (part of the HOW series) on the best practices for performance optimization for Intel® Xeon Phi processor family x200 (formerly Knights Landing). In this 2-hour webinar we will highlight the new processor features andperform hands-on

A PERFORMANCE-BASED COMPARISON OF C/C++ COMPILERS MODERN CODE FOR INTEL XEON PHI PROCESSORS This series of 45-minute webinars was presented by Colfax International in collaboration with Intel in 2016. Part 1 | Part 2 | Part 3 1. Strategies for Multi-Threading on Intel Xeon Phi Proce OPTIMIZATION OF REAL-TIME OBJECT DETECTION ON INTEL® XEON1. REAL-TIME OBJECT DETECTION2. TENSORFLOW AND MKL3. OPTIMIZATION OF CNN3.1. YOLOSEE MORE ON COLFAXRESEARCH.COM HOW NEW QLC SATA SSDS DELIVER 8X FASTER MACHINE LEARNING Table 1: System Configuration. 4. Test Workload: TFRecord. TFRecord is the standard format for TensorFlow. It is used to store large amounts of data (for example, a collection of images) in a single TFRecord file, which can be read from storage faster than individual files and loaded into TensorFlow in batches for training. HPLINPACK BENCHMARK ON INTEL XEON PHI PROCESSOR FAMILYSECTION 1. HPLINPACK BENCHMARKALGORITHMHPL CONFIGURATION FILESECTION 2. SYSTEM CONFIGURATIONSEE MORE ON COLFAXRESEARCH.COM MC² 003: PLASMA SIMULATION WITH PARTICLE-IN-CELL CODE CFHall is a plasma simulation code based on a particle-in-cell method. It uses the finite difference method on a rectangular mesh for Maxwell equations, and couples it to superparticle traversal the mesh in a self-consistent approach. The uniqueness of CFHall lies in the use of the Locally Recursive non-Locally Asynchronous (LRnLA) algorithms. A SURVEY AND BENCHMARKS OF INTEL® XEON® GOLD AND PLATINUM1. WHICH XEON IS RIGHT FOR YOU?2. CPU COMPARISON FOR DIFFERENT WORKLOADS2.4. BANDWIDTH-LIMITED3. PROCESSOR CHOICE RECOMMENDATIONSSEE MORE ONCOLFAXRESEARCH.COM

GUIDE TO AUTOMATIC VECTORIZATION WITH INTEL AVX-5121. VECTOR INSTRUCTIONS2. STRUCTURE AND FUNCTIONALITY OF AVX-5122.1. SUBSETS2.2. AVX512-FSEE MORE ON COLFAXRESEARCH.COM RESEARCH PUBLICATIONS We regularly publish white papers and research publications on HPC-related technology and methods. Explore our knowledge base in this catalog of categories or visit the Archive (chronological order TRAINING | COLFAX RESEARCH The workshop includes 20 hours of instruction and code for hands-on exercises. This training is free to everyone thanks to Intel’s sponsorship. You can access the video recordings of lectures, slides of presentations and code of practical exercises on this page using a free Colfax Research account. To run the hands-on exercises, you willneed

MODERN CODE FOR INTEL XEON PHI PROCESSORS This series of 45-minute webinars was presented by Colfax International in collaboration with Intel in 2016. Part 1 | Part 2 | Part 3 1. Strategies for Multi-Threading on Intel Xeon Phi Proce AN OPTIMIZATION APPROACH FOR AGENT-BASED COMPUTATIONAL a Software Performance Optimization Group, Imperial College London, London, United Kingdom b CERN Openlab, IT Department, CERN, Switzerland c Intel Corporation, USA d Colfax International, USA e Interdisciplinary Computing and Complex BioSystems Research Group, School of Computing, Newcastle University, Newcastle upon Tyne, United Kingdom f Institute of Neuroscience, Newcastle University HOW NEW QLC SATA SSDS DELIVER 8X FASTER MACHINE LEARNING Table 1: System Configuration. 4. Test Workload: TFRecord. TFRecord is the standard format for TensorFlow. It is used to store large amounts of data (for example, a collection of images) in a single TFRecord file, which can be read from storage faster than individual files and loaded into TensorFlow in batches for training. INTRODUCTION TO INTEL DAAL, PART 1: POLYNOMIAL REGRESSION This is the part 1 of 3 of an introductory series of publications on the Intel Data Analytics Acceleration Library (DAAL). DAAL is a data analytics library optimized for modern highly parallel computer architectures such as Intel Xeon and Intel Xeon Phi processors. A SURVEY AND BENCHMARKS OF INTEL® XEON® GOLD AND PLATINUM For example, the 2-socket system with Intel Xeon Gold processor 6128 has a total of 12 cores, and the measured performance is 90% of the expectation. In contrast, the same 2-socket system with Intel Xeon Platinum processor 8160 has 48 cores and performs at CAPABILITIES OF INTEL® AVX-512 IN INTEL® XEON® SCALABLE Later, in 2017, AVX-512 was used in Intel® Xeon® processor Scalable family (formerly Skylake). The most notable new feature of AVX-512 compared to AVX/AVX2 is the 512-bit vector register width, which is twice the size of the AVX/AVX2 registers. However, AVX-512 is more than just a promotion of the vector register width from 256 to 512bits.

MC² 002: COMD, MOLECULAR DYNAMICS PROXY A case study on software modernization using CoMD – a Molecular Dynamics Proxy Application. An integral part of the procurement of newer computer hardware is the accompanied software modernization. In particular, the recent release of many-core architecture has required rethinking the process of software development.MEET US AT SC16

If you are going to the SC16 conference, visit Colfax:. At the Intel HPC Developer Conference (free pre-SC16 event) When: on Sunday, November 13, 2016, at 9:45 am – 10:35 am Where: Sheraton Salt Lake City Hotel Event: Technical session “Optimizing Machine Learning Workloads on Intel Platforms” On the SC’16 exhibition floor When: Monday, November 14 through Thursday, November 16COLFAX RESEARCH

Best Practices for Speed in Deep Learning Applications on Intel Architecture. An optimization approach for agent-based computational models of biological development. Optimization of Real-Time Object Detection on Intel® Xeon® Scalable Processors. A Performance-Based Comparison of C/C++ Compilers. TRAINING | COLFAX RESEARCH As the leading provider of code modernization and optimization training, Colfax now offers a hands-on workshop (part of the HOW series) on the best practices for performance optimization for Intel® Xeon Phi processor family x200 (formerly Knights Landing). In this 2-hour webinar we will highlight the new processor features andperform hands-on

A PERFORMANCE-BASED COMPARISON OF C/C++ COMPILERS AN OPTIMIZATION APPROACH FOR AGENT-BASED COMPUTATIONAL a Software Performance Optimization Group, Imperial College London, London, United Kingdom b CERN Openlab, IT Department, CERN, Switzerland c Intel Corporation, USA d Colfax International, USA e Interdisciplinary Computing and Complex BioSystems Research Group, School of Computing, Newcastle University, Newcastle upon Tyne, United Kingdom f Institute of Neuroscience, Newcastle University OPTIMIZATION OF REAL-TIME OBJECT DETECTION ON INTEL® XEON1. REAL-TIME OBJECT DETECTION2. TENSORFLOW AND MKL3. OPTIMIZATION OF CNN3.1. YOLOSEE MORE ON COLFAXRESEARCH.COM FALCON LIBRARY: FAST IMAGE CONVOLUTION IN NEURAL NETWORKSSECTION 1. CONVOLUTION IN MACHINE LEARNINGSECTION 2. WINOGRAD'S MINIMAL FIR FILTERINGSECTION 3. APPLICATION TO CONVNETSSECTION 4. TRANSFORMATION TO GEMMSEE MORE ON COLFAXRESEARCH.COM HPLINPACK BENCHMARK ON INTEL XEON PHI PROCESSOR FAMILYSECTION 1. HPLINPACK BENCHMARKALGORITHMHPL CONFIGURATION FILESECTION 2. SYSTEM CONFIGURATIONSEE MORE ON COLFAXRESEARCH.COM HOW NEW QLC SATA SSDS DELIVER 8X FASTER MACHINE LEARNING Table 1: System Configuration. 4. Test Workload: TFRecord. TFRecord is the standard format for TensorFlow. It is used to store large amounts of data (for example, a collection of images) in a single TFRecord file, which can be read from storage faster than individual files and loaded into TensorFlow in batches for training. GUIDE TO AUTOMATIC VECTORIZATION WITH INTEL AVX-5121. VECTOR INSTRUCTIONS2. STRUCTURE AND FUNCTIONALITY OF AVX-5122.1. SUBSETS2.2. AVX512-FSEE MORE ON COLFAXRESEARCH.COM CLUSTERING MODES IN KNIGHTS LANDING PROCESSORSCOLFAX RESEARCH

Best Practices for Speed in Deep Learning Applications on Intel Architecture. An optimization approach for agent-based computational models of biological development. Optimization of Real-Time Object Detection on Intel® Xeon® Scalable Processors. A Performance-Based Comparison of C/C++ Compilers. TRAINING | COLFAX RESEARCH As the leading provider of code modernization and optimization training, Colfax now offers a hands-on workshop (part of the HOW series) on the best practices for performance optimization for Intel® Xeon Phi processor family x200 (formerly Knights Landing). In this 2-hour webinar we will highlight the new processor features andperform hands-on

A PERFORMANCE-BASED COMPARISON OF C/C++ COMPILERS AN OPTIMIZATION APPROACH FOR AGENT-BASED COMPUTATIONAL a Software Performance Optimization Group, Imperial College London, London, United Kingdom b CERN Openlab, IT Department, CERN, Switzerland c Intel Corporation, USA d Colfax International, USA e Interdisciplinary Computing and Complex BioSystems Research Group, School of Computing, Newcastle University, Newcastle upon Tyne, United Kingdom f Institute of Neuroscience, Newcastle University OPTIMIZATION OF REAL-TIME OBJECT DETECTION ON INTEL® XEON1. REAL-TIME OBJECT DETECTION2. TENSORFLOW AND MKL3. OPTIMIZATION OF CNN3.1. YOLOSEE MORE ON COLFAXRESEARCH.COM FALCON LIBRARY: FAST IMAGE CONVOLUTION IN NEURAL NETWORKSSECTION 1. CONVOLUTION IN MACHINE LEARNINGSECTION 2. WINOGRAD'S MINIMAL FIR FILTERINGSECTION 3. APPLICATION TO CONVNETSSECTION 4. TRANSFORMATION TO GEMMSEE MORE ON COLFAXRESEARCH.COM HPLINPACK BENCHMARK ON INTEL XEON PHI PROCESSOR FAMILYSECTION 1. HPLINPACK BENCHMARKALGORITHMHPL CONFIGURATION FILESECTION 2. SYSTEM CONFIGURATIONSEE MORE ON COLFAXRESEARCH.COM HOW NEW QLC SATA SSDS DELIVER 8X FASTER MACHINE LEARNING Table 1: System Configuration. 4. Test Workload: TFRecord. TFRecord is the standard format for TensorFlow. It is used to store large amounts of data (for example, a collection of images) in a single TFRecord file, which can be read from storage faster than individual files and loaded into TensorFlow in batches for training. GUIDE TO AUTOMATIC VECTORIZATION WITH INTEL AVX-5121. VECTOR INSTRUCTIONS2. STRUCTURE AND FUNCTIONALITY OF AVX-5122.1. SUBSETS2.2. AVX512-FSEE MORE ON COLFAXRESEARCH.COM CLUSTERING MODES IN KNIGHTS LANDING PROCESSORS TRAINING | COLFAX RESEARCH Optimization for Intel Xeon Phi Processors x200. As the leading provider of code modernization and optimization training, Colfax now offers a hands-on workshop (part of the HOW series) on the best practices for performance optimization for Intel® Xeon Phi processor family x200 (formerly Knights Landing).In this 2-hour webinar we will highlight the new processor features and perform hands-on AN OPTIMIZATION APPROACH FOR AGENT-BASED COMPUTATIONAL a Software Performance Optimization Group, Imperial College London, London, United Kingdom b CERN Openlab, IT Department, CERN, Switzerland c Intel Corporation, USA d Colfax International, USA e Interdisciplinary Computing and Complex BioSystems Research Group, School of Computing, Newcastle University, Newcastle upon Tyne, United Kingdom f Institute of Neuroscience, Newcastle University HOW SERIES “DEEP DIVE”: WEBINARS ON PERFORMANCE HOW Series “Deep Dive” is a free Web-based training on parallel programming and performance optimization on Intel architecture. The workshop includes 20 hours of instruction and code for hands-on exercises. This training is free to everyone thanks to Intel’s sponsorship. You can access the video recordings of lectures, slidesof

CUSTOM TRAINING

How to Get in Touch. We are located at 2805 Bowers Ave, Santa Clara, California 95051, USA. Reach us by phone 1-408-730-2275 or via email: team@colfaxresearch.com. Share this: LinkedIn. Twitter. Facebook.More. Tumblr.

MC² SERIES: MODERN CODE CONTRIBUTED TALKS In Modern Code Contributed Talks, or MC² Series, experts in computational disciplines share their experience. Register for these ongoing webinars to learn the performance optimization methods used in real-life applications. INTRODUCTION TO INTEL DAAL, PART 1: POLYNOMIAL REGRESSION This is the part 1 of 3 of an introductory series of publications on the Intel Data Analytics Acceleration Library (DAAL). DAAL is a data analytics library optimized for modern highly parallel computer architectures such as Intel Xeon and Intel Xeon Phi processors. MC² 003: PLASMA SIMULATION WITH PARTICLE-IN-CELL CODE CFHall is a plasma simulation code based on a particle-in-cell method. It uses the finite difference method on a rectangular mesh for Maxwell equations, and couples it to superparticle traversal the mesh in a self-consistent approach. The uniqueness of CFHall lies in the use of the Locally Recursive non-Locally Asynchronous (LRnLA) algorithms. OPTIMIZATION OF HAMERLY’S K-MEANS CLUSTERING ALGORITHM This publication describes the application of performance optimizations techniques to Hamerly’s K-means clustering algorithm. Starting with an unoptimized implementation of the algorithm, we discuss: Presented optimizations aggregate to 85.6x speedup comparedto

A SURVEY AND BENCHMARKS OF INTEL® XEON® GOLD AND PLATINUM For example, the 2-socket system with Intel Xeon Gold processor 6128 has a total of 12 cores, and the measured performance is 90% of the expectation. In contrast, the same 2-socket system with Intel Xeon Platinum processor 8160 has 48 cores and performs at INTEL® PYTHON* ON 2ND GENERATION INTEL® XEON PHI 1. A Case for Python in Computing. Python is a popular scripting language in computational applications. Empowered with the fundamental tools for scientific computing, NumPy and SciPy libraries, Python applications can express in brief and convenient form basic linear algebra subroutines (BLAS) and linear algebra package (LAPACK) functions for operations on matrices and systems of linearCOLFAX RESEARCH

Best Practices for Speed in Deep Learning Applications on Intel Architecture. An optimization approach for agent-based computational models of biological development. Optimization of Real-Time Object Detection on Intel® Xeon® Scalable Processors. A Performance-Based Comparison of C/C++ Compilers. TRAINING | COLFAX RESEARCH As the leading provider of code modernization and optimization training, Colfax now offers a hands-on workshop (part of the HOW series) on the best practices for performance optimization for Intel® Xeon Phi processor family x200 (formerly Knights Landing). In this 2-hour webinar we will highlight the new processor features andperform hands-on

A PERFORMANCE-BASED COMPARISON OF C/C++ COMPILERS AN OPTIMIZATION APPROACH FOR AGENT-BASED COMPUTATIONAL a Software Performance Optimization Group, Imperial College London, London, United Kingdom b CERN Openlab, IT Department, CERN, Switzerland c Intel Corporation, USA d Colfax International, USA e Interdisciplinary Computing and Complex BioSystems Research Group, School of Computing, Newcastle University, Newcastle upon Tyne, United Kingdom f Institute of Neuroscience, Newcastle University OPTIMIZATION OF REAL-TIME OBJECT DETECTION ON INTEL® XEON1. REAL-TIME OBJECT DETECTION2. TENSORFLOW AND MKL3. OPTIMIZATION OF CNN3.1. YOLOSEE MORE ON COLFAXRESEARCH.COM FALCON LIBRARY: FAST IMAGE CONVOLUTION IN NEURAL NETWORKSSECTION 1. CONVOLUTION IN MACHINE LEARNINGSECTION 2. WINOGRAD'S MINIMAL FIR FILTERINGSECTION 3. APPLICATION TO CONVNETSSECTION 4. TRANSFORMATION TO GEMMSEE MORE ON COLFAXRESEARCH.COM HPLINPACK BENCHMARK ON INTEL XEON PHI PROCESSOR FAMILYSECTION 1. HPLINPACK BENCHMARKALGORITHMHPL CONFIGURATION FILESECTION 2. SYSTEM CONFIGURATIONSEE MORE ON COLFAXRESEARCH.COM HOW NEW QLC SATA SSDS DELIVER 8X FASTER MACHINE LEARNING Table 1: System Configuration. 4. Test Workload: TFRecord. TFRecord is the standard format for TensorFlow. It is used to store large amounts of data (for example, a collection of images) in a single TFRecord file, which can be read from storage faster than individual files and loaded into TensorFlow in batches for training. GUIDE TO AUTOMATIC VECTORIZATION WITH INTEL AVX-5121. VECTOR INSTRUCTIONS2. STRUCTURE AND FUNCTIONALITY OF AVX-5122.1. SUBSETS2.2. AVX512-FSEE MORE ON COLFAXRESEARCH.COM CLUSTERING MODES IN KNIGHTS LANDING PROCESSORSCOLFAX RESEARCH

Best Practices for Speed in Deep Learning Applications on Intel Architecture. An optimization approach for agent-based computational models of biological development. Optimization of Real-Time Object Detection on Intel® Xeon® Scalable Processors. A Performance-Based Comparison of C/C++ Compilers. TRAINING | COLFAX RESEARCH As the leading provider of code modernization and optimization training, Colfax now offers a hands-on workshop (part of the HOW series) on the best practices for performance optimization for Intel® Xeon Phi processor family x200 (formerly Knights Landing). In this 2-hour webinar we will highlight the new processor features andperform hands-on

A PERFORMANCE-BASED COMPARISON OF C/C++ COMPILERS AN OPTIMIZATION APPROACH FOR AGENT-BASED COMPUTATIONAL a Software Performance Optimization Group, Imperial College London, London, United Kingdom b CERN Openlab, IT Department, CERN, Switzerland c Intel Corporation, USA d Colfax International, USA e Interdisciplinary Computing and Complex BioSystems Research Group, School of Computing, Newcastle University, Newcastle upon Tyne, United Kingdom f Institute of Neuroscience, Newcastle University OPTIMIZATION OF REAL-TIME OBJECT DETECTION ON INTEL® XEON1. REAL-TIME OBJECT DETECTION2. TENSORFLOW AND MKL3. OPTIMIZATION OF CNN3.1. YOLOSEE MORE ON COLFAXRESEARCH.COM FALCON LIBRARY: FAST IMAGE CONVOLUTION IN NEURAL NETWORKSSECTION 1. CONVOLUTION IN MACHINE LEARNINGSECTION 2. WINOGRAD'S MINIMAL FIR FILTERINGSECTION 3. APPLICATION TO CONVNETSSECTION 4. TRANSFORMATION TO GEMMSEE MORE ON COLFAXRESEARCH.COM HPLINPACK BENCHMARK ON INTEL XEON PHI PROCESSOR FAMILYSECTION 1. HPLINPACK BENCHMARKALGORITHMHPL CONFIGURATION FILESECTION 2. SYSTEM CONFIGURATIONSEE MORE ON COLFAXRESEARCH.COM HOW NEW QLC SATA SSDS DELIVER 8X FASTER MACHINE LEARNING Table 1: System Configuration. 4. Test Workload: TFRecord. TFRecord is the standard format for TensorFlow. It is used to store large amounts of data (for example, a collection of images) in a single TFRecord file, which can be read from storage faster than individual files and loaded into TensorFlow in batches for training. GUIDE TO AUTOMATIC VECTORIZATION WITH INTEL AVX-5121. VECTOR INSTRUCTIONS2. STRUCTURE AND FUNCTIONALITY OF AVX-5122.1. SUBSETS2.2. AVX512-FSEE MORE ON COLFAXRESEARCH.COM CLUSTERING MODES IN KNIGHTS LANDING PROCESSORS TRAINING | COLFAX RESEARCH Optimization for Intel Xeon Phi Processors x200. As the leading provider of code modernization and optimization training, Colfax now offers a hands-on workshop (part of the HOW series) on the best practices for performance optimization for Intel® Xeon Phi processor family x200 (formerly Knights Landing).In this 2-hour webinar we will highlight the new processor features and perform hands-on AN OPTIMIZATION APPROACH FOR AGENT-BASED COMPUTATIONAL a Software Performance Optimization Group, Imperial College London, London, United Kingdom b CERN Openlab, IT Department, CERN, Switzerland c Intel Corporation, USA d Colfax International, USA e Interdisciplinary Computing and Complex BioSystems Research Group, School of Computing, Newcastle University, Newcastle upon Tyne, United Kingdom f Institute of Neuroscience, Newcastle University HOW SERIES “DEEP DIVE”: WEBINARS ON PERFORMANCE Register; Why Attend; Roadmap; Instructor; Prerequisites; Cluster; Materials; Book . In a Nutshell. HOW Series “Deep Dive” is a free Web-based training on parallel programming and performance optimization on Intel architecture. The workshop includes 20 hours of instruction and code for hands-on exercises. This training is free to everyone thanks to Intel’s sponsorship. MC² SERIES: MODERN CODE CONTRIBUTED TALKS In Modern Code Contributed Talks, or MC² Series, experts in computational disciplines share their experience. Register for these ongoing webinars to learn the performance optimization methods used in real-life applications.CUSTOM TRAINING

We are known worldwide for our public training programs on parallel programming, performance optimization and modern code practices. We conduct web-based training (e.g., HOW Series “Deep Dive INTRODUCTION TO INTEL DAAL, PART 1: POLYNOMIAL REGRESSION This is the part 1 of 3 of an introductory series of publications on the Intel Data Analytics Acceleration Library (DAAL). DAAL is a data analytics library optimized for modern highly parallel computer architectures such as Intel Xeon and Intel Xeon Phi processors. OPTIMIZATION OF HAMERLY’S K-MEANS CLUSTERING ALGORITHM Here, both delta_member_vector_sum and delta_member_counter are declared inside the parallel region, and both of these variables are thread-private arrays. After all the work has been completed, the OpenMP pragma atomic is used to safely combine all the thread-private results into a single master result. Note that both delta_member_vector_sum and delta_member_counter were MC² 003: PLASMA SIMULATION WITH PARTICLE-IN-CELL CODE Presentation. Particle-in-cell Code with LRnLA Algorithms, Performance Tests on KNL. CFHall is a plasma simulation code based on a particle-in-cell method. INTEL® PYTHON* ON 2ND GENERATION INTEL® XEON PHI 1. A Case for Python in Computing. Python is a popular scripting language in computational applications. Empowered with the fundamental tools for scientific computing, NumPy and SciPy libraries, Python applications can express in brief and convenient form basic linear algebra subroutines (BLAS) and linear algebra package (LAPACK) functions for operations on matrices and systems of linear A SURVEY AND BENCHMARKS OF INTEL® XEON® GOLD AND PLATINUM Table 2: The clock frequencies of the top 24 models relevant to the most important usage scenarios. C is the number of cores per socket, B is the base frequency for scalar workloads (the number that you will find in most documents), T S is the maximum Turbo frequency for scalar workloads on 1 core, T PS is for scalar workloads on C cores, and T PV is for AVX-512 workloads on C cores.MENU

*

* Research ►

* Publications by Date * Publications Categories ►* Benchmarks

* Case Studies

* Development Tools

* HPC System Administration* Machine Learning

* Technology Exploration* Training ►

* Training

* HOW Series “Deep Dive” * HOW Series “KNL” * HOW Series “Tools”* MC² Series

* Modern Code Webinars * Parallelism on IA (Coursera) * Presentations, Interviews, Demos* Services ►

* Overview

* Consulting

* Commissioned Research* Custom Training

* Hosting

* About Us ►

* Colfax Research

* Team

* Newsletter

* Support

* Terms of Service

*

Welcome! You are viewing archived content of the Colfax Research project. For our current business page, see colfax-intl.com*

*

* Research

* Publications by Date * Publications Categories* Benchmarks

* Case Studies

* Development Tools

* HPC System Administration* Machine Learning

* Technology Exploration* Training

* Training

* HOW Series “Deep Dive” * HOW Series “KNL” * HOW Series “Tools”* MC² Series

* Modern Code Webinars * Parallelism on IA (Coursera) * Presentations, Interviews, Demos* Services

* Overview

* Consulting

* Commissioned Research* Custom Training

* Hosting

* About Us

* Colfax Research

* Team

* Newsletter

* Support

* Terms of Service

*

*

*

*

*

*

*

RECENT

*

Canonical Stratification for Non-Mathematicians*

How New QLC SATA SSDs Deliver 8x Faster Machine Learning*

Best Practices for Speed in Deep Learning Applications on IntelArchitecture

*

An optimization approach for agent-based computational models of biological development*

Optimization of Real-Time Object Detection on Intel® Xeon® ScalableProcessors

*

A Performance-Based Comparison of C/C++ CompilersRESEARCH

We regularly publish white papers, research articles, programming tutorials and technical recipes. See our publication archive for details. You can also commission our research.

To Publications

TRAINING

Learn about modern code methods, get certified in performance optimization, listen to guest speakers’ technology adoption stories. We also conduct custom training .Training Calendar

SERVICES

Colfax Research offers consulting and training on software modernization and performance tuning, commissioned research , and hosting for specialized computing resources.Our Services

MENU

* Support

* Terms of Service

* Support

* Terms of Service

Copyright © 2011-2018 Colfax InternationalDetails

Copyright © 2024 ArchiveBay.com. All rights reserved. Terms of Use | Privacy Policy | DMCA | 2021 | Feedback | Advertising | RSS 2.0