Are you over 18 and want to see adult content?

More Annotations

A complete backup of didacticamultimedia.com

Are you over 18 and want to see adult content?

A complete backup of nothingbutcomics.net

Are you over 18 and want to see adult content?

A complete backup of konanmedical.com

Are you over 18 and want to see adult content?

A complete backup of rafmaelumat.blogspot.com

Are you over 18 and want to see adult content?

A complete backup of laptopbatteryonline.net

Are you over 18 and want to see adult content?

A complete backup of minimum-wage.org

Are you over 18 and want to see adult content?

Favourite Annotations

Mountain Home Photo | Aspen Colorado Real Estate Photography

Are you over 18 and want to see adult content?

Recipe This | Smart Parents Use Gadgets

Are you over 18 and want to see adult content?

صفحة روابط التحميل السريع

Are you over 18 and want to see adult content?

Water-Efficient Commercial Bathroom Products | Sloan

Are you over 18 and want to see adult content?

会社を辞めた時に受け取れるものが失業保険(失業給付)です。手続きから約立つ情報を提供しています。 - 知らないと損する雇用保険(失業保険)

Are you over 18 and want to see adult content?

بيت الزملكاوية الموقع الأكبر و الاشهر لجماهير الزمالك

Are you over 18 and want to see adult content?

Luxury Park Farm Hotel | Norwich | Norfolk | Best Price Promise

Are you over 18 and want to see adult content?

BallerStatus.com | News, Culture & Lifestyle

Are you over 18 and want to see adult content?

Oracle Marketing Cloud and Data Cloud Privacy Policy | Oracle

Are you over 18 and want to see adult content?

Online812.ru - сетевой журнал горячих политических вопросов

Are you over 18 and want to see adult content?

Text

Online-Seminar.

IPC-DOKUMENTE

IPC-A-600 - Abnahmekriterien für Leiterplatten. IPC-7711/21 - Nacharbeit, Änderung und Reparatur von elektronischen Baugruppe. J-STD-001 - Anforderungen an gelötete elektrische und elektronische Baugruppen. IPC-6012 - Qualifikation und Leistungsspezifikation für starre Leiterplatten. IPC-2221 - Grundrichtlinie für das Design vonLeiterplatten.

IPC SCHULUNGEN

Deutschsprachige Schulungen zum CIS oder CIT auf Basis der internation anerkannten Richtlinien IPC-A-600, IPC-A-610, IPC/WHMA-A-620,J-STD-001, 7711/21.

3D-DESIGN IN CADENCE ALLEGRO / ORCAD FlowCAD om 1 FlowCAD 3D-Design in Cadence Allegro / OrCAD Holger Schröter FED Regionalgruppe Stuttgart 12.04.2017 SEMINARE REFLOWLÖTEN MIT DR. HANS BELL Reflowlöten. Neue Seminarreihe mit Dr. Hans Bell. Seit mehr als 40 Jahren werden elektronische Baugruppen mit Hilfe des Reflowlötens gefertigt, welches sich zum weltweit dominanten Fertigungsverfahren im Bereich des Weichlötens entwickelt hat. Über die Jahrzehnte hat es mit der stetigen Miniaturisierung und der komplexen Bestückung von HIGH-POWER-BAUGRUPPEN-DESIGN High-Power-Baugruppen-Design. Antriebstechnologien, alternative Energieerzeugung oder e-Mobilität eint die Tatsache, dass die Spannung bis weit über 230 V liegt und Ströme dauerhaft über 20 A teilweise bis über 100 A fließen. Um dies technisch zu realisieren, wurden in der Vergangenheit häufig diskrete Aufbauten genutzt.REFLOWLÖTEN

Herr Dr. rer. nat. Hans Bell war bis 2020 Leiter der Entwicklung und Technologie bei der Firma Rehm Thermal Systems GmbH in Blaubeuren-Seissen. An der Humboldt-Universität zu Berlin hat er Physik / Kristallographie studiert und an der TU München promoviert. Bis 1999 war er für die Firmen WF und DeTeWe in Berlin als Technologetätig und dort

RECOMMENDATIONS OF THE FED AND ZVEI ON MULTIPLE SOLDER LIMITS 3. Results The following recommendations apply to rigid PCBs. In the case of special forms (flex, rigid-flex, IMS) and special materials (e.g. polymide), the soldering parameters must be agreed BELASTBARKEIT VON LEITERBAHNEN AUF UND IN LEITERPLATTEN Belastbarkeit von Leiterbahnen auf und in Leiterplatten © Lothar Oberender, 08.11.2018 6 Bild 5-7 Leiter auf Innen-und Außenlagen (ruhende Luft) (0,001 -0,5 mm²) HOME | FACHVERBAND ELEKTRONIK-DESIGN (FED) E.V.TRANSLATE THIS PAGE Ihr Fachverband für Design, Leiterplatten- und Elektronikfertigung ist Partner für die gesamte Elektronikindustrie mit Angeboten zur beruflichen Aus- und Weiterbildung, Publikationen, Dokumenten und IPC-Richtlinien. Durch die Förderung des Erfahrungsaustausches leistet der FED einen wesentlichen Beitrag zur Wettbewerbsfähigkeit der Elektronikbranche. SEMINARE | FACHVERBAND ELEKTRONIK-DESIGN (FED) E.V.TRANSLATE THIS PAGE Seminare. In unseren ein- und mehrtägigen Seminaren vermitteln wir Ihnen Grundkenntnisse und Spezialwissen in den Bereichen Leiterplattendesign bzw. Elektronikdesign und -fertigung.Online-Seminar.

IPC-DOKUMENTE

IPC-A-600 - Abnahmekriterien für Leiterplatten. IPC-7711/21 - Nacharbeit, Änderung und Reparatur von elektronischen Baugruppe. J-STD-001 - Anforderungen an gelötete elektrische und elektronische Baugruppen. IPC-6012 - Qualifikation und Leistungsspezifikation für starre Leiterplatten. IPC-2221 - Grundrichtlinie für das Design vonLeiterplatten.

IPC SCHULUNGEN

Deutschsprachige Schulungen zum CIS oder CIT auf Basis der internation anerkannten Richtlinien IPC-A-600, IPC-A-610, IPC/WHMA-A-620,J-STD-001, 7711/21.

3D-DESIGN IN CADENCE ALLEGRO / ORCAD FlowCAD om 1 FlowCAD 3D-Design in Cadence Allegro / OrCAD Holger Schröter FED Regionalgruppe Stuttgart 12.04.2017 SEMINARE REFLOWLÖTEN MIT DR. HANS BELL Reflowlöten. Neue Seminarreihe mit Dr. Hans Bell. Seit mehr als 40 Jahren werden elektronische Baugruppen mit Hilfe des Reflowlötens gefertigt, welches sich zum weltweit dominanten Fertigungsverfahren im Bereich des Weichlötens entwickelt hat. Über die Jahrzehnte hat es mit der stetigen Miniaturisierung und der komplexen Bestückung von HIGH-POWER-BAUGRUPPEN-DESIGN High-Power-Baugruppen-Design. Antriebstechnologien, alternative Energieerzeugung oder e-Mobilität eint die Tatsache, dass die Spannung bis weit über 230 V liegt und Ströme dauerhaft über 20 A teilweise bis über 100 A fließen. Um dies technisch zu realisieren, wurden in der Vergangenheit häufig diskrete Aufbauten genutzt.REFLOWLÖTEN

Herr Dr. rer. nat. Hans Bell war bis 2020 Leiter der Entwicklung und Technologie bei der Firma Rehm Thermal Systems GmbH in Blaubeuren-Seissen. An der Humboldt-Universität zu Berlin hat er Physik / Kristallographie studiert und an der TU München promoviert. Bis 1999 war er für die Firmen WF und DeTeWe in Berlin als Technologetätig und dort

RECOMMENDATIONS OF THE FED AND ZVEI ON MULTIPLE SOLDER LIMITS 3. Results The following recommendations apply to rigid PCBs. In the case of special forms (flex, rigid-flex, IMS) and special materials (e.g. polymide), the soldering parameters must be agreed BELASTBARKEIT VON LEITERBAHNEN AUF UND IN LEITERPLATTEN Belastbarkeit von Leiterbahnen auf und in Leiterplatten © Lothar Oberender, 08.11.2018 6 Bild 5-7 Leiter auf Innen-und Außenlagen (ruhende Luft) (0,001 -0,5 mm²) FED-SHOP | FACHVERBAND ELEKTRONIK-DESIGN (FED) E.V. Dietmar Baar. Technische Redaktion und Beratung. Tel. +49 30 340 6030-54. E-Mail senden. APPLICATION AND UTILISATION OF PROTECTIVE COATINGS An electronic module is only suitable for a specific purpose if it guarantees safe function for a defined time. A large number of modules are installed in the terminal devices without protective coatings and operate fault-free throughout their entire service life. In an increasing number of cases, the module is used with greater electrical sensitivity or even under difficult conditions. IPC-7621 (PDF) SINGLE USER IPC-7621 (PDF) Single User Guideline for Design, Material Selection and General Application of Encapsulation of Electronic Circuit Assembly by Low Pressure Molding with Thermoplastics BAUGRUPPE | FACHVERBAND ELEKTRONIK-DESIGN (FED) E.V. Baugruppe: Eine Reihe von miteinander verbundenen (elektronischen) Bau(Teilen), Unterbaugruppen oder Kombinationen daraus. (Anmerkung: Dieser Begriff kann auch in Verbindung mit anderen Begriffen, z.B. Bestückte Leiterplatte, verwendet werden.) assembly, assembled board: number of parts, subassemblies or combinations thereof joined together printed board, PB, board, card, circuit card THE REALITY ABOUT ENERGY HARVESTING � All rights reserved by Würth Elektronik eiSos GmbH & Co.KG, also in the event of industrial property rights. All rights of disposalsuch as copying and

BOROWSKI FED ROADSHOW 2019 7', 3ur]hvvru )3*$ 887 32:(5-7$* 5$0 65$0 '5$0 ''5 5$0 3dudoohohu )/$6+ 1$1' 125 $ ' & $ ' & $ ' & &/. ',63/$< o 2 /$1 86% 3&,h 6$7$ ' $ j 2q &+,3)/$6+ &" / r# 2#$ " ÿFED.DE

Moved Permanently. The document has moved here. BAUGRUPPENPRODUKTION SCHULUNGSFILM Der FED hat im Rahmen seiner Aus- und Weiterbildungsaktivitäten einen Lehrfilm zur Baugruppenfertigung produziert. Anlass für dieses Projekt ist der groîe Bedarf, Mitarbeitern Kenntnisse über den Produktionsprozess von elektronischen Baugruppen zu vermitteln. PRÄSENTATION KONTRON ELECTRONICS 10 Features • Standard sizes: 7 ^ (1024 x 600) 10.1 ^ (1280 x 800) 15.6 ^ (1388 x 768) • High-quality displays : same display types as the Control Panels • Touch: Capacitive Multitouch PCAP • Premium Design : same mechanical design as the Control Panels Front : slim aluminum or stainless steel frame Backside: robust stainless steel housing with pre-mounted clamping elements NIEDRIGSCHMELZENDE LOTMATERIALIEN AELSOLD Bismut — Fazit Zusammenfassung Deutschland ist weltweit drittgrößter Absatzmarkt für Bismut. Bismut ist weder typisches Industrie-, noch Hightech-, sondern Sondermetall. HOME | FACHVERBAND ELEKTRONIK-DESIGN (FED) E.V.TRANSLATE THIS PAGE Ihr Fachverband für Design, Leiterplatten- und Elektronikfertigung ist Partner für die gesamte Elektronikindustrie mit Angeboten zur beruflichen Aus- und Weiterbildung, Publikationen, Dokumenten und IPC-Richtlinien. Durch die Förderung des Erfahrungsaustausches leistet der FED einen wesentlichen Beitrag zur Wettbewerbsfähigkeit der Elektronikbranche.IPC-DOKUMENTE

IPC-A-600 - Abnahmekriterien für Leiterplatten. IPC-7711/21 - Nacharbeit, Änderung und Reparatur von elektronischen Baugruppe. J-STD-001 - Anforderungen an gelötete elektrische und elektronische Baugruppen. IPC-6012 - Qualifikation und Leistungsspezifikation für starre Leiterplatten. IPC-2221 - Grundrichtlinie für das Design vonLeiterplatten.

SEMINARE | FACHVERBAND ELEKTRONIK-DESIGN (FED) E.V.TRANSLATE THIS PAGE Seminare. In unseren ein- und mehrtägigen Seminaren vermitteln wir Ihnen Grundkenntnisse und Spezialwissen in den Bereichen Leiterplattendesign bzw. Elektronikdesign und -fertigung.Online-Seminar.

IPC SCHULUNGEN

Deutschsprachige Schulungen zum CIS oder CIT auf Basis der internation anerkannten Richtlinien IPC-A-600, IPC-A-610, IPC/WHMA-A-620,J-STD-001, 7711/21.

SEMINARE REFLOWLÖTEN MIT DR. HANS BELL Reflowlöten. Neue Seminarreihe mit Dr. Hans Bell. Seit mehr als 40 Jahren werden elektronische Baugruppen mit Hilfe des Reflowlötens gefertigt, welches sich zum weltweit dominanten Fertigungsverfahren im Bereich des Weichlötens entwickelt hat. Über die Jahrzehnte hat es mit der stetigen Miniaturisierung und der komplexen Bestückung von HIGH-POWER-BAUGRUPPEN-DESIGN High-Power-Baugruppen-Design. Antriebstechnologien, alternative Energieerzeugung oder e-Mobilität eint die Tatsache, dass die Spannung bis weit über 230 V liegt und Ströme dauerhaft über 20 A teilweise bis über 100 A fließen. Um dies technisch zu realisieren, wurden in der Vergangenheit häufig diskrete Aufbauten genutzt.REFLOWLÖTEN

Herr Dr. rer. nat. Hans Bell war bis 2020 Leiter der Entwicklung und Technologie bei der Firma Rehm Thermal Systems GmbH in Blaubeuren-Seissen. An der Humboldt-Universität zu Berlin hat er Physik / Kristallographie studiert und an der TU München promoviert. Bis 1999 war er für die Firmen WF und DeTeWe in Berlin als Technologetätig und dort

RECOMMENDATIONS OF THE FED AND ZVEI ON MULTIPLE SOLDER LIMITS 3. Results The following recommendations apply to rigid PCBs. In the case of special forms (flex, rigid-flex, IMS) and special materials (e.g. polymide), the soldering parameters must be agreed MAGI³C POWER MODULE � All rights reserved by Wurth Elektronik, also in the event of industrial property rights. All rights of disposal such as copying and redistribution rights with us. BELASTBARKEIT VON LEITERBAHNEN AUF UND IN LEITERPLATTEN Belastbarkeit von Leiterbahnen auf und in Leiterplatten © Lothar Oberender, 08.11.2018 6 Bild 5-7 Leiter auf Innen-und Außenlagen (ruhende Luft) (0,001 -0,5 mm²) HOME | FACHVERBAND ELEKTRONIK-DESIGN (FED) E.V.TRANSLATE THIS PAGE Ihr Fachverband für Design, Leiterplatten- und Elektronikfertigung ist Partner für die gesamte Elektronikindustrie mit Angeboten zur beruflichen Aus- und Weiterbildung, Publikationen, Dokumenten und IPC-Richtlinien. Durch die Förderung des Erfahrungsaustausches leistet der FED einen wesentlichen Beitrag zur Wettbewerbsfähigkeit der Elektronikbranche.IPC-DOKUMENTE

IPC-A-600 - Abnahmekriterien für Leiterplatten. IPC-7711/21 - Nacharbeit, Änderung und Reparatur von elektronischen Baugruppe. J-STD-001 - Anforderungen an gelötete elektrische und elektronische Baugruppen. IPC-6012 - Qualifikation und Leistungsspezifikation für starre Leiterplatten. IPC-2221 - Grundrichtlinie für das Design vonLeiterplatten.

SEMINARE | FACHVERBAND ELEKTRONIK-DESIGN (FED) E.V.TRANSLATE THIS PAGE Seminare. In unseren ein- und mehrtägigen Seminaren vermitteln wir Ihnen Grundkenntnisse und Spezialwissen in den Bereichen Leiterplattendesign bzw. Elektronikdesign und -fertigung.Online-Seminar.

IPC SCHULUNGEN

Deutschsprachige Schulungen zum CIS oder CIT auf Basis der internation anerkannten Richtlinien IPC-A-600, IPC-A-610, IPC/WHMA-A-620,J-STD-001, 7711/21.

SEMINARE REFLOWLÖTEN MIT DR. HANS BELL Reflowlöten. Neue Seminarreihe mit Dr. Hans Bell. Seit mehr als 40 Jahren werden elektronische Baugruppen mit Hilfe des Reflowlötens gefertigt, welches sich zum weltweit dominanten Fertigungsverfahren im Bereich des Weichlötens entwickelt hat. Über die Jahrzehnte hat es mit der stetigen Miniaturisierung und der komplexen Bestückung von HIGH-POWER-BAUGRUPPEN-DESIGN High-Power-Baugruppen-Design. Antriebstechnologien, alternative Energieerzeugung oder e-Mobilität eint die Tatsache, dass die Spannung bis weit über 230 V liegt und Ströme dauerhaft über 20 A teilweise bis über 100 A fließen. Um dies technisch zu realisieren, wurden in der Vergangenheit häufig diskrete Aufbauten genutzt.REFLOWLÖTEN

Herr Dr. rer. nat. Hans Bell war bis 2020 Leiter der Entwicklung und Technologie bei der Firma Rehm Thermal Systems GmbH in Blaubeuren-Seissen. An der Humboldt-Universität zu Berlin hat er Physik / Kristallographie studiert und an der TU München promoviert. Bis 1999 war er für die Firmen WF und DeTeWe in Berlin als Technologetätig und dort

RECOMMENDATIONS OF THE FED AND ZVEI ON MULTIPLE SOLDER LIMITS 3. Results The following recommendations apply to rigid PCBs. In the case of special forms (flex, rigid-flex, IMS) and special materials (e.g. polymide), the soldering parameters must be agreed MAGI³C POWER MODULE � All rights reserved by Wurth Elektronik, also in the event of industrial property rights. All rights of disposal such as copying and redistribution rights with us. BELASTBARKEIT VON LEITERBAHNEN AUF UND IN LEITERPLATTEN Belastbarkeit von Leiterbahnen auf und in Leiterplatten © Lothar Oberender, 08.11.2018 6 Bild 5-7 Leiter auf Innen-und Außenlagen (ruhende Luft) (0,001 -0,5 mm²) FED-SHOP | FACHVERBAND ELEKTRONIK-DESIGN (FED) E.V.TRANSLATE THIS PAGE FED-22-12 Papierversion Entscheidungshilfe für die Auswahl und Einführung bzw. Ablösung eines EDA-Systems Stand: September 2002 Innerhalb eines FED-Projektes hat eine Arbeitsgruppe eine von Firmen und Systemen unabhängigen Empfehlung erarbeitet, die den kompletten Ablauf von der Feststellung der Notwendigkeit eines neues EDA-System bis zur Einführung desselben beschreibt.REFLOWLÖTEN

Herr Dr. rer. nat. Hans Bell war bis 2020 Leiter der Entwicklung und Technologie bei der Firma Rehm Thermal Systems GmbH in Blaubeuren-Seissen. An der Humboldt-Universität zu Berlin hat er Physik / Kristallographie studiert und an der TU München promoviert. Bis 1999 war er für die Firmen WF und DeTeWe in Berlin als Technologetätig und dort

ESD-SEMINARE

Dieses wird in den Seminaren des FED e.V. durch fachkundige Seminarleiter vermittelt. Das Seminarpaket des FED e.V. ist charakterisiert durch eine fachlich integere Vermittlung von Spezialwissen, einen hohen Grad an Aktualität und Praxisverbundenheit sowie den konsequenten Verzicht auf die Bewerbung selektierterESD-Produkte.

HIGH-POWER-BAUGRUPPEN-DESIGN High-Power-Baugruppen-Design. Antriebstechnologien, alternative Energieerzeugung oder e-Mobilität eint die Tatsache, dass die Spannung bis weit über 230 V liegt und Ströme dauerhaft über 20 A teilweise bis über 100 A fließen. Um dies technisch zu realisieren, wurden in der Vergangenheit häufig diskrete Aufbauten genutzt. ROHS ANHANG II: ÜBERARBEITUNG DER LISTE BESCHRÄNKTER STOFFE Dr. Otmar Deubzer Dept. Environmental & Reliability Engineering © Fraunhofer IZM 1 RoHS Anhang II: Überarbeitung der Liste beschränkter Stoffe SCHAEFFLER UNTERNEHMENSPRÄSENTATION A l l e R e c h t e v o r b e h a l t e n f ü r S c h a e f f l e r T e c h n o l o g i e s A G & C o. K G, i n s b e s o n d e r e f ü r d e n F a l l e i n e r S GRUNDLAGEN DER MODERNEN BAUGRUPPENFERTIGUNG Grundlagen der modernen Baugruppenfertigung. Die moderne Fertigung von Baugruppen stellt immer höhere Ansprüche an die Prozesse der Aufbau- und Verbindungstechnik. So müssen Prozesse in zunehmendem Umfang produktspezifisch qualifiziert werden, da Standardprozesse nicht mehrausreichend sind.

IST INTERCONNECT STRESS TEST Widerstandserhöhung durch therm. Belastung: RESISTANCE DEGRADATION OF THE PTH INTERCONNECT-10 0 10 20 30 40 50 1 16 31 46 61 76 91 106 121 136 151 166 181 196 211 226 241 256 271 286 301 316 331 346 361 376391

QUALITÄT UND ZUVERLÄSSIGKEIT VON LEITERPLATTEN UND …TRANSLATE THISPAGE

Durch die Reduzierung der Strukturgrößen und die Erhöhung der Packungsdichte steigen die Anforderungen an Leiterplatten und Baugruppen. Das betrifft sowohl die Anforderungen an die Lötbarkeit der Leiterplattenoberflächen als auch die Anforderungen an die Eigenschaften der Isolierstoffe von Basismaterial und Lötstoppmaske. UL 746 + IPC 4101E „WAS IST NEU?“ SPITZENLAMINATE UND PREPREGS – AUF JEDE ANFORDERUNG ZUGESCHNITTEN Technolam Business Training UL 746 + IPC 4101E „Was ist NEU?“ HOME | FACHVERBAND ELEKTRONIK-DESIGN (FED) E.V.TRANSLATE THIS PAGE Ihr Fachverband für Design, Leiterplatten- und Elektronikfertigung ist Partner für die gesamte Elektronikindustrie mit Angeboten zur beruflichen Aus- und Weiterbildung, Publikationen, Dokumenten und IPC-Richtlinien. Durch die Förderung des Erfahrungsaustausches leistet der FED einen wesentlichen Beitrag zur Wettbewerbsfähigkeit der Elektronikbranche. FED-SHOP | FACHVERBAND ELEKTRONIK-DESIGN (FED) E.V.TRANSLATE THIS PAGE FED-22-12 Papierversion Entscheidungshilfe für die Auswahl und Einführung bzw. Ablösung eines EDA-Systems Stand: September 2002 Innerhalb eines FED-Projektes hat eine Arbeitsgruppe eine von Firmen und Systemen unabhängigen Empfehlung erarbeitet, die den kompletten Ablauf von der Feststellung der Notwendigkeit eines neues EDA-System bis zur Einführung desselben beschreibt. SEMINARE | FACHVERBAND ELEKTRONIK-DESIGN (FED) E.V.TRANSLATE THIS PAGE Seminare. In unseren ein- und mehrtägigen Seminaren vermitteln wir Ihnen Grundkenntnisse und Spezialwissen in den Bereichen Leiterplattendesign bzw. Elektronikdesign und -fertigung.Online-Seminar.

IPC-DOKUMENTE

IPC-A-600 - Abnahmekriterien für Leiterplatten. IPC-7711/21 - Nacharbeit, Änderung und Reparatur von elektronischen Baugruppe. J-STD-001 - Anforderungen an gelötete elektrische und elektronische Baugruppen. IPC-6012 - Qualifikation und Leistungsspezifikation für starre Leiterplatten. IPC-2221 - Grundrichtlinie für das Design vonLeiterplatten.

IPC SCHULUNGEN

Deutschsprachige Schulungen zum CIS oder CIT auf Basis der internation anerkannten Richtlinien IPC-A-600, IPC-A-610, IPC/WHMA-A-620,J-STD-001, 7711/21.

3D-DESIGN IN CADENCE ALLEGRO / ORCAD FlowCAD om 1 FlowCAD 3D-Design in Cadence Allegro / OrCAD Holger Schröter FED Regionalgruppe Stuttgart 12.04.2017 HIGH-POWER-BAUGRUPPEN-DESIGN High-Power-Baugruppen-Design. Antriebstechnologien, alternative Energieerzeugung oder e-Mobilität eint die Tatsache, dass die Spannung bis weit über 230 V liegt und Ströme dauerhaft über 20 A teilweise bis über 100 A fließen. Um dies technisch zu realisieren, wurden in der Vergangenheit häufig diskrete Aufbauten genutzt. SEMINARE REFLOWLÖTEN MIT DR. HANS BELL Reflowlöten. Neue Seminarreihe mit Dr. Hans Bell. Seit mehr als 40 Jahren werden elektronische Baugruppen mit Hilfe des Reflowlötens gefertigt, welches sich zum weltweit dominanten Fertigungsverfahren im Bereich des Weichlötens entwickelt hat. Über die Jahrzehnte hat es mit der stetigen Miniaturisierung und der komplexen Bestückung von MAGI³C POWER MODULE � All rights reserved by Wurth Elektronik, also in the event of industrial property rights. All rights of disposal such as copying and redistribution rights with us. ROHS ANHANG II: ÜBERARBEITUNG DER LISTE BESCHRÄNKTER STOFFE Dr. Otmar Deubzer Dept. Environmental & Reliability Engineering © Fraunhofer IZM 1 RoHS Anhang II: Überarbeitung der Liste beschränkter Stoffe HOME | FACHVERBAND ELEKTRONIK-DESIGN (FED) E.V.TRANSLATE THIS PAGE Ihr Fachverband für Design, Leiterplatten- und Elektronikfertigung ist Partner für die gesamte Elektronikindustrie mit Angeboten zur beruflichen Aus- und Weiterbildung, Publikationen, Dokumenten und IPC-Richtlinien. Durch die Förderung des Erfahrungsaustausches leistet der FED einen wesentlichen Beitrag zur Wettbewerbsfähigkeit der Elektronikbranche. FED-SHOP | FACHVERBAND ELEKTRONIK-DESIGN (FED) E.V.TRANSLATE THIS PAGE FED-22-12 Papierversion Entscheidungshilfe für die Auswahl und Einführung bzw. Ablösung eines EDA-Systems Stand: September 2002 Innerhalb eines FED-Projektes hat eine Arbeitsgruppe eine von Firmen und Systemen unabhängigen Empfehlung erarbeitet, die den kompletten Ablauf von der Feststellung der Notwendigkeit eines neues EDA-System bis zur Einführung desselben beschreibt. SEMINARE | FACHVERBAND ELEKTRONIK-DESIGN (FED) E.V.TRANSLATE THIS PAGE Seminare. In unseren ein- und mehrtägigen Seminaren vermitteln wir Ihnen Grundkenntnisse und Spezialwissen in den Bereichen Leiterplattendesign bzw. Elektronikdesign und -fertigung.Online-Seminar.

IPC-DOKUMENTE

IPC-A-600 - Abnahmekriterien für Leiterplatten. IPC-7711/21 - Nacharbeit, Änderung und Reparatur von elektronischen Baugruppe. J-STD-001 - Anforderungen an gelötete elektrische und elektronische Baugruppen. IPC-6012 - Qualifikation und Leistungsspezifikation für starre Leiterplatten. IPC-2221 - Grundrichtlinie für das Design vonLeiterplatten.

IPC SCHULUNGEN

Deutschsprachige Schulungen zum CIS oder CIT auf Basis der internation anerkannten Richtlinien IPC-A-600, IPC-A-610, IPC/WHMA-A-620,J-STD-001, 7711/21.

3D-DESIGN IN CADENCE ALLEGRO / ORCAD FlowCAD om 1 FlowCAD 3D-Design in Cadence Allegro / OrCAD Holger Schröter FED Regionalgruppe Stuttgart 12.04.2017 HIGH-POWER-BAUGRUPPEN-DESIGN High-Power-Baugruppen-Design. Antriebstechnologien, alternative Energieerzeugung oder e-Mobilität eint die Tatsache, dass die Spannung bis weit über 230 V liegt und Ströme dauerhaft über 20 A teilweise bis über 100 A fließen. Um dies technisch zu realisieren, wurden in der Vergangenheit häufig diskrete Aufbauten genutzt. SEMINARE REFLOWLÖTEN MIT DR. HANS BELL Reflowlöten. Neue Seminarreihe mit Dr. Hans Bell. Seit mehr als 40 Jahren werden elektronische Baugruppen mit Hilfe des Reflowlötens gefertigt, welches sich zum weltweit dominanten Fertigungsverfahren im Bereich des Weichlötens entwickelt hat. Über die Jahrzehnte hat es mit der stetigen Miniaturisierung und der komplexen Bestückung von MAGI³C POWER MODULE � All rights reserved by Wurth Elektronik, also in the event of industrial property rights. All rights of disposal such as copying and redistribution rights with us. ROHS ANHANG II: ÜBERARBEITUNG DER LISTE BESCHRÄNKTER STOFFE Dr. Otmar Deubzer Dept. Environmental & Reliability Engineering © Fraunhofer IZM 1 RoHS Anhang II: Überarbeitung der Liste beschränkter Stoffe HOME | FACHVERBAND ELEKTRONIK-DESIGN (FED) E.V.TRANSLATE THIS PAGE Ihr Fachverband für Design, Leiterplatten- und Elektronikfertigung ist Partner für die gesamte Elektronikindustrie mit Angeboten zur beruflichen Aus- und Weiterbildung, Publikationen, Dokumenten und IPC-Richtlinien. Durch die Förderung des Erfahrungsaustausches leistet der FED einen wesentlichen Beitrag zur Wettbewerbsfähigkeit der Elektronikbranche. FED-SHOP | FACHVERBAND ELEKTRONIK-DESIGN (FED) E.V.TRANSLATE THIS PAGE FED-22-12 Papierversion Entscheidungshilfe für die Auswahl und Einführung bzw. Ablösung eines EDA-Systems Stand: September 2002 Innerhalb eines FED-Projektes hat eine Arbeitsgruppe eine von Firmen und Systemen unabhängigen Empfehlung erarbeitet, die den kompletten Ablauf von der Feststellung der Notwendigkeit eines neues EDA-System bis zur Einführung desselben beschreibt. HIGH-POWER-BAUGRUPPEN-DESIGN High-Power-Baugruppen-Design. Antriebstechnologien, alternative Energieerzeugung oder e-Mobilität eint die Tatsache, dass die Spannung bis weit über 230 V liegt und Ströme dauerhaft über 20 A teilweise bis über 100 A fließen. Um dies technisch zu realisieren, wurden in der Vergangenheit häufig diskrete Aufbauten genutzt.REFLOWLÖTEN

Herr Dr. rer. nat. Hans Bell war bis 2020 Leiter der Entwicklung und Technologie bei der Firma Rehm Thermal Systems GmbH in Blaubeuren-Seissen. An der Humboldt-Universität zu Berlin hat er Physik / Kristallographie studiert und an der TU München promoviert. Bis 1999 war er für die Firmen WF und DeTeWe in Berlin als Technologetätig und dort

ZED LEVEL II

ZED Level II - Leiterplatten-Baugruppendesign 1. Ein wesentlicher inhaltlicher Schwerpunkt des Kurses ist die Vermittlung der technologischen Kompetenz für produktionsgerechtes Design. Ein weiterer, die Vorbereitung des Designers auf seine zentrale Rolle innerhalb der Wertschöpfungskette und damit auf alle Phasen des Produktkreationsprozesses. SCHAEFFLER UNTERNEHMENSPRÄSENTATION A l l e R e c h t e v o r b e h a l t e n f ü r S c h a e f f l e r T e c h n o l o g i e s A G & C o. K G, i n s b e s o n d e r e f ü r d e n F a l l e i n e r S RECOMMENDATIONS OF THE FED AND ZVEI ON MULTIPLE SOLDER LIMITS 3. Results The following recommendations apply to rigid PCBs. In the case of special forms (flex, rigid-flex, IMS) and special materials (e.g. polymide), the soldering parameters must be agreed IST INTERCONNECT STRESS TEST Widerstandserhöhung durch therm. Belastung: RESISTANCE DEGRADATION OF THE PTH INTERCONNECT-10 0 10 20 30 40 50 1 16 31 46 61 76 91 106 121 136 151 166 181 196 211 226 241 256 271 286 301 316 331 346 361 376391

BELASTBARKEIT VON LEITERBAHNEN AUF UND IN LEITERPLATTEN Belastbarkeit von Leiterbahnen auf und in Leiterplatten © Lothar Oberender, 08.11.2018 6 Bild 5-7 Leiter auf Innen-und Außenlagen (ruhende Luft) (0,001 -0,5 mm²) UL 746 + IPC 4101E „WAS IST NEU?“ SPITZENLAMINATE UND PREPREGS – AUF JEDE ANFORDERUNG ZUGESCHNITTEN Technolam Business Training UL 746 + IPC 4101E „Was ist NEU?“ HOME | FACHVERBAND ELEKTRONIK-DESIGN (FED) E.V. Ihr Fachverband für Design, Leiterplatten- und Elektronikfertigung ist Partner für die gesamte Elektronikindustrie mit Angeboten zur beruflichen Aus- und Weiterbildung, Publikationen, Dokumenten und IPC-Richtlinien. Durch die Förderung des Erfahrungsaustausches leistet der FED einen wesentlichen Beitrag zur Wettbewerbsfähigkeit der Elektronikbranche.IPC-DOKUMENTE

Richtlinien und Revisionen. IPC-DRM-SMT-G - Surface Mount Solder Joint Evaluation Training & Reference Guide; IPC-DRM-PTH-G - Through-Hole Solder Joint Evaluation Training & Reference Guide; IPC/PERM-2901 - Pb-free Design and Assembly Implementation Guide; IPC-7094A-Design and Assembly Process Implementation for Flip Chip and Die-Size Components; IPC-7621 - Guideline for Design, Material SEMINARE | FACHVERBAND ELEKTRONIK-DESIGN (FED) E.V. Grundlagen und Spezialwissen-Seminare zu Themen des Elektronik-Designs und der Elektronikfertigung.IPC SCHULUNGEN

Deutschsprachige Schulungen zum CIS oder CIT auf Basis der internation anerkannten Richtlinien IPC-A-600, IPC-A-610, IPC/WHMA-A-620,J-STD-001, 7711/21.

ESD-SEMINARE

Systematische Ausbildung von ESD-Schutz-Fachkräften - ESD-Schutzmanagement, ESD-Messpraktikum, Ausbildung zum ESD-Auditor HIGH-POWER-BAUGRUPPEN-DESIGN Michael Schleicher hat 1991 als "Leiterplattenkonstrukteur" seine ersten Layouts auf PC-basierenden Systemen erstellt.Als Absolvent der Fachschule für Leiterplattentechnik arbeitet er in unterschiedlichen Unternehmen im Bereich Leiterplattenlayout, Baugruppendesign.ZED LEVEL II

ZED Level II - Leiterplatten-Baugruppendesign 1 Leiterplattendesign leiterplattendesign.de leiterplattendesign.orgREFLOWLÖTEN

Herr Dr. rer. nat. Hans Bell war bis 2020 Leiter der Entwicklung und Technologie bei der Firma Rehm Thermal Systems GmbH inBlaubeuren-Seissen.

SCHAEFFLER UNTERNEHMENSPRÄSENTATION A l l e R e c h t e v o r b e h a l t e n f ü r S c h a e f f l e r T e c h n o l o g i e s A G & C o. K G, i n s b e s o n d e r e f ü r d e n F a l l e i n e r S MAGI³C POWER MODULE � All rights reserved by Wurth Elektronik, also in the event of industrial property rights. All rights of disposal such as copying and redistribution rights with us. HOME | FACHVERBAND ELEKTRONIK-DESIGN (FED) E.V. Ihr Fachverband für Design, Leiterplatten- und Elektronikfertigung ist Partner für die gesamte Elektronikindustrie mit Angeboten zur beruflichen Aus- und Weiterbildung, Publikationen, Dokumenten und IPC-Richtlinien. Durch die Förderung des Erfahrungsaustausches leistet der FED einen wesentlichen Beitrag zur Wettbewerbsfähigkeit der Elektronikbranche.IPC-DOKUMENTE

Richtlinien und Revisionen. IPC-DRM-SMT-G - Surface Mount Solder Joint Evaluation Training & Reference Guide; IPC-DRM-PTH-G - Through-Hole Solder Joint Evaluation Training & Reference Guide; IPC/PERM-2901 - Pb-free Design and Assembly Implementation Guide; IPC-7094A-Design and Assembly Process Implementation for Flip Chip and Die-Size Components; IPC-7621 - Guideline for Design, Material SEMINARE | FACHVERBAND ELEKTRONIK-DESIGN (FED) E.V. Grundlagen und Spezialwissen-Seminare zu Themen des Elektronik-Designs und der Elektronikfertigung.IPC SCHULUNGEN

Deutschsprachige Schulungen zum CIS oder CIT auf Basis der internation anerkannten Richtlinien IPC-A-600, IPC-A-610, IPC/WHMA-A-620,J-STD-001, 7711/21.

ESD-SEMINARE

Systematische Ausbildung von ESD-Schutz-Fachkräften - ESD-Schutzmanagement, ESD-Messpraktikum, Ausbildung zum ESD-Auditor HIGH-POWER-BAUGRUPPEN-DESIGN Michael Schleicher hat 1991 als "Leiterplattenkonstrukteur" seine ersten Layouts auf PC-basierenden Systemen erstellt.Als Absolvent der Fachschule für Leiterplattentechnik arbeitet er in unterschiedlichen Unternehmen im Bereich Leiterplattenlayout, Baugruppendesign.ZED LEVEL II

ZED Level II - Leiterplatten-Baugruppendesign 1 Leiterplattendesign leiterplattendesign.de leiterplattendesign.orgREFLOWLÖTEN

Herr Dr. rer. nat. Hans Bell war bis 2020 Leiter der Entwicklung und Technologie bei der Firma Rehm Thermal Systems GmbH inBlaubeuren-Seissen.

SCHAEFFLER UNTERNEHMENSPRÄSENTATION A l l e R e c h t e v o r b e h a l t e n f ü r S c h a e f f l e r T e c h n o l o g i e s A G & C o. K G, i n s b e s o n d e r e f ü r d e n F a l l e i n e r S MAGI³C POWER MODULE � All rights reserved by Wurth Elektronik, also in the event of industrial property rights. All rights of disposal such as copying and redistribution rights with us. FED-SHOP | FACHVERBAND ELEKTRONIK-DESIGN (FED) E.V. FED-22-12 Papierversion Entscheidungshilfe für die Auswahl und Einführung bzw. Ablösung eines EDA-Systems Stand: September 2002 Innerhalb eines FED-Projektes hat eine Arbeitsgruppe eine von Firmen und Systemen unabhängigen Empfehlung erarbeitet, die den kompletten Ablauf von der Feststellung der Notwendigkeit eines neues EDA-System bis zur Einführung desselben beschreibt.ESD-SEMINARE

Systematische Ausbildung von ESD-Schutz-Fachkräften - ESD-Schutzmanagement, ESD-Messpraktikum, Ausbildung zum ESD-AuditorZED LEVEL I

Teil 1 und 2 des Kurses schließen jeweils mit einer Prüfung ab. Nach Bestehen der Prüfungen erlangen die Teilnehmer den Abschluss Zertifizierter Elektronik-Designer ZED Level I.. Damit erlangen die Teilnehmer die erste Stufe einer anerkannten beruflichen Qualifikation, die ihnen eine optimale Ausgangsposition für die Karriere in einer Branche mit Zukunft gewährt.ZED LEVEL II

ZED Level II - Leiterplatten-Baugruppendesign 1 Leiterplattendesign leiterplattendesign.de leiterplattendesign.org EMV-BAUGRUPPEN-DESIGN SEMINAR EMV-Seminar zur Behandlung von Abstrahlungsmechanismen, Grundlagen elektromagnetischer Felder, Praktische Übungen für Schaltungsentwickler und LeiterplattenREFLOWLÖTEN

Das Seminar diskutiert die Wechselwirkung der Verbindungspartner bei der Entstehung einer Lötstelle. Dabei stehen die Benetzungsvorgänge und die unterschiedlichen Eigenschaften von Loten und lötbaren Oberflächen im Fokus. SEMINARE REFLOWLÖTEN MIT DR. HANS BELL Der FED betrachtet es als Aufgabe und Verpflichtung, durch Angebote zur beruflichen Aus- und Weiterbildung, durch die Bereitstellung praxisnaher IPC-Richtlinien und durch die Förderung des Erfahrungsaustausches einen wesentlichen Beitrag zur Wettbewerbsfähigkeit der Elektronikbranche zuEMV - FED

EMC-K FED Regionalgruppe Schweiz / EMV 27.06.2018 12 Ziele des EMV-Designs Platzieren der Schaltkreis und ihrer Komponenten (billigste EMV-Massnahme) IST INTERCONNECT STRESS TEST Widerstandserhöhung durch therm. Belastung: RESISTANCE DEGRADATION OF THE PTH INTERCONNECT-10 0 10 20 30 40 50 1 16 31 46 61 76 91 106 121 136 151 166 181 196 211 226 241 256 271 286 301 316 331 346 361 376391

BELASTBARKEIT VON LEITERBAHNEN AUF UND IN LEITERPLATTEN Belastbarkeit von Leiterbahnen auf und in Leiterplatten © Lothar Oberender, 08.11.2018 6 Bild 5-7 Leiter auf Innen-und Außenlagen (ruhende Luft) (0,001 -0,5 mm²) Diese Webseite verwendet Cookies zur Optimierung der Webseitennutzung. Einzelheiten über die von uns eingesetzten Cookies finden Sie in unseren Datenschutzbestimmungen.Schließen

WIR SUCHEN DIE BESTEN LEITERPLATTEN-DESIGNER Die Frist wurde verlängert: Jetzt bis 7. Juni 2020 Design-Projekt einreichen und gewinnen!Mehr

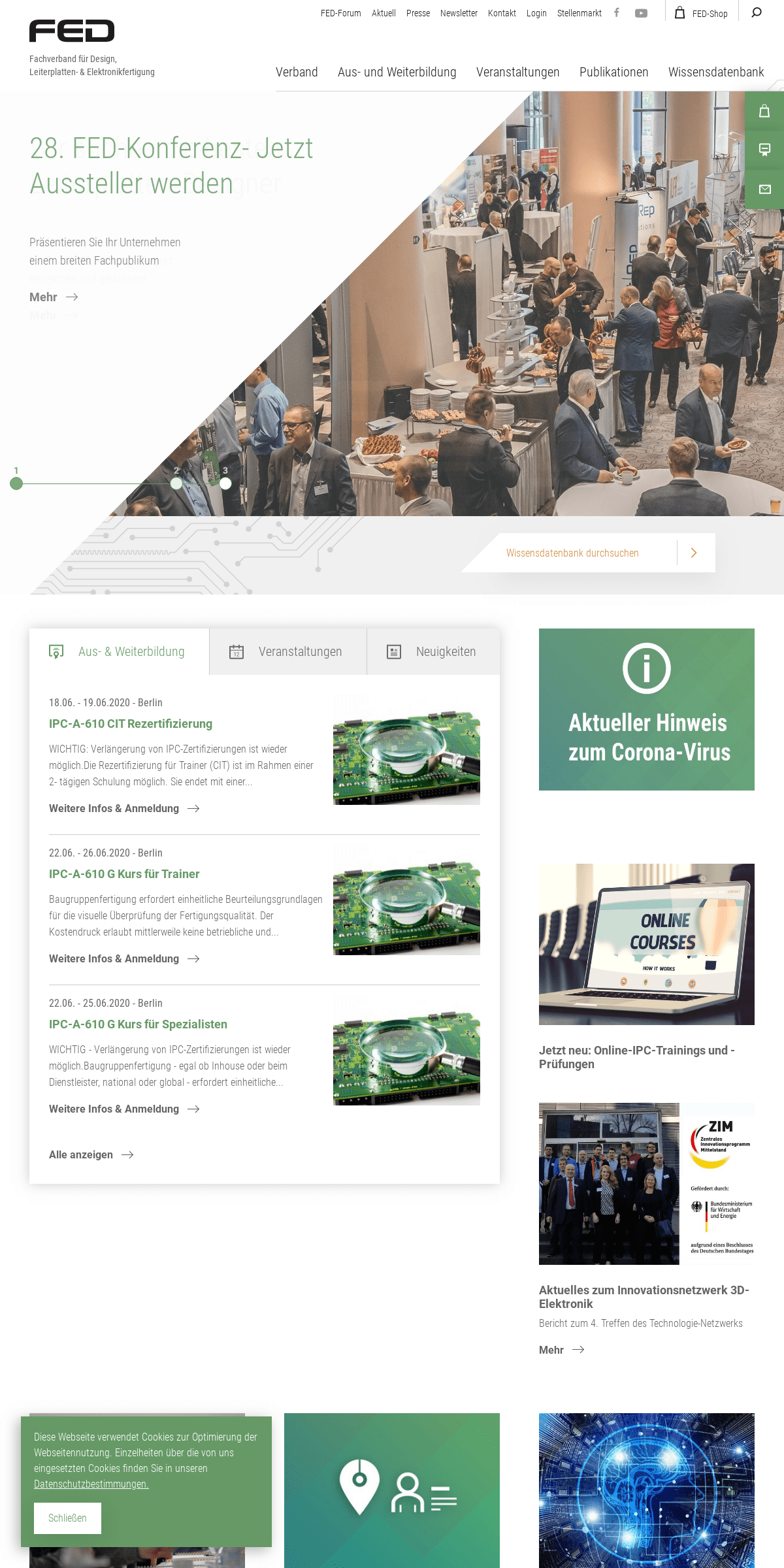

28. FED-KONFERENZ- JETZT AUSSTELLER WERDEN Präsentieren Sie Ihr Unternehmen einem breiten FachpublikumMehr

ZERTIFIZIERTER ELEKTRONIK-DESIGNER (ZED) Mit dem vierstufigen Schulungskonzept "Zertifizierter Elektronik-Designer (ZED)" erhöht der FED die berufliche Kompetenz und Akzeptanz von Leiterplatten-Designern. Die Absolventen erlangen fachliches Grund- und Spezialwissen über Leiterplatten- undBaugruppendesign.

Mehr

* 1

* 2

* 3

3/3

* Aus- & Weiterbildung* Veranstaltungen

* Neuigkeiten

Aus- & Weiterbildung 18.06. - 19.06.2020 - Berlin IPC-A-610 CIT REZERTIFIZIERUNG WICHTIG: Verlängerung von IPC-Zertifizierungen ist wieder möglich.Die Rezertifizierung für Trainer (CIT) ist im Rahmen einer 2- tägigen Schulung möglich. Sie endet mit einer... Weitere Infos & Anmeldung 22.06. - 26.06.2020 - Berlin IPC-A-610 G KURS FÜR TRAINER Baugruppenfertigung erfordert einheitliche Beurteilungsgrundlagen für die visuelle Überprüfung der Fertigungsqualität. Der Kostendruck erlaubt mittlerweile keine betriebliche und... Weitere Infos & Anmeldung 22.06. - 25.06.2020 - Berlin IPC-A-610 G KURS FÜR SPEZIALISTEN WICHTIG - Verlängerung von IPC-Zertifizierungen ist wieder möglich.Baugruppenfertigung - egal ob Inhouse oder beim Dienstleister, national oder global - erfordert einheitliche... Weitere Infos & AnmeldungAlle anzeigen

Veranstaltungen

� Fotograf / Agentur 03.06.2020Online WebinarFED FED-REGIONALGRUPPE HAMBURG - QUALIFIZIERTE REWORKPROZESSE Von der Anforderung zum sicheren und dokumentierten Prozess Weitere Infos & Anmeldung � Fotograf / Agentur 03.06.2020Online WebinarFED FED-REGIONALGRUPPE STUTTGART - "KURZ & KNACKIG" - TEIL 3 Überblick zur Lötstoppmaske in digitaler Additivtechnik bis hin zur funktionellen 3D-Oberfläche Weitere Infos & Anmeldung � Fotograf / Agentur 18.06.2020Online WebinarFED FED-REGIONALGRUPPE BERLIN Lösungen zur Qualitätssicherung und Langzeitlagerung von Bauteilen in Zeiten der Allokation Weitere Infos & AnmeldungAlle anzeigen

Neuigkeiten

� Fotograf / Agentur27.05.2020FED

AKTUELLER HINWEIS ZUM CORONA-VIRUS Dem FED sind die Gesundheit und Sicherheit seiner Seminarteilnehmerinnen und -teilnehmer ein großes Anliegen. Bitte beachten Sie daher die folgenden Hinweise. Ab Juni 2020 werden wirunsere...

Mehr

� Fotograf / Agentur06.05.2020Berlin

BERICHT ZUM 4. TREFFEN DES TECHNOLOGIE-NETZWERKS 3D-ELEKTRONIK Das vom FED initiierte Technologienetzwerk 3D-Elektronik hat am 29. April 2020 sein viertes Netzwerktreffen veranstaltet. Statt der geplanten Tagung am Fraunhofer-Institut ENAS in Paderborn hatte der Organisator Jöckel Innovation Consulting (JÖIN) zu einem virtuellen Meeting eingeladen. Ein neues Mitglied, die Start-up NanoWired GmbH, und ein Gastunternehmen erhielten die Gelegenheit, ihre Firmen vorzustellen und über herausragende neue Technologien zu berichten. Insgesamt nahmen fünf Unternehmen, zwei Fraunhofer-Institute sowie die TU Dresden an der Online-Veranstaltung teil.Mehr

� Fotograf / Agentur29.04.2020FED

IPC-SCHULUNGEN JETZT AUCH ONLINE Aufgrund der Einschränkungen durch die Corona-Krise bietet der FED ab sofort Online-Trainings und -Prüfungen an.Mehr

Alle anzeigen

JETZT NEU: ONLINE-IPC-TRAININGS UND -PRÜFUNGEN AKTUELLES ZUM INNOVATIONSNETZWERK 3D-ELEKTRONIK Bericht zum 4. Treffen des Technologie-NetzwerksMehr

� FED

FED-INHOUSE-SCHULUNGEN Sie können viele FED-Kurse und -Seminare auch als Inhouse-Schulungbuchen

Mehr

MITGLIEDER- UND DIENSTLEISTERÜBERSICHT Sie suchen einen Designdienstleister oder Leiterplatten- und Baugruppenhersteller in Ihrer Nähe? Hier finden Sie ihn.Mehr

JETZT AUS- UND WEITERBILDUNG STARTEN Finden Sie Ihre passende WeiterbildungMehr

JETZT MITGLIED WERDEN * Plattform für Branchen-Networking * Austausch mit Fachexperten * Umfangreiches Schulungsangebot * Zugang zu Arbeitskreisen und Projektgruppen * Diskussion und Weiterbildung in Regionalgruppen * Vergünstigte Preise für Veranstaltungen und Schulungen * Vielfältige Serviceleistungen Jetzt Mitglied werdenNEWSLETTER

Vorname

Nachname

E-Mail*

Abonnieren

MITGLIEDER

*

*

*

*

*

*

*

*

*

*

*

*

*

*

*

*

*

*

*

*

*

*

*

*

*

*

*

*

*

*

*

*

*

*

*

*

*

*

*

*

*

*

*

*

*

*

*

*

*

*

*

*

*

*

*

*

*

*

*

*

*

*

*

*

*

*

*

*

*

*

*

*

*

*

*

*

*

*

*

*

*

*

*

*

*

*

*

*

*

*

*

*

*

*

*

*

*

*

*

*

*

*

*

*

*

*

*

*

*

*

*

*

*

*

*

*

*

*

*

*

*

*

*

*

*

*

*

*

*

*

*

*

*

*

*

*

*

*

*

*

*

*

*

*

*

*

*

*

*

*

*

*

*

*

*

*

*

*

*

*

*

*

*

*

*

*

*

*

*

*

*

*

*

*

*

*

*

*

*

*

*

*

*

*

*

*

*

*

*

*

*

*

*

*

*

*

Navigation öffnen

Menü Navigation schließenNavigation schließen * VerbandUnternavigation öffnen ZurückNavigation schließen * Verband* Über uns

* Mitglied werden

* RegionalgruppenUnternavigation öffnen ZurückNavigation schließen * Regionalgruppen* Berlin

* Dresden

* Düsseldorf

* Frankfurt a. Main

* Hamburg

* Hannover

* Jena

* München

* Nürnberg

* Stuttgart

* Österreich

* Schweiz

* ArbeitskreiseUnternavigation öffnen ZurückNavigation schließen * Arbeitskreise * Arbeitskreis Nachwuchsgewinnung * Arbeitskreis 3D-Elektronik * Arbeitskreis Leiterplatte * Arbeitskreis Normen und Richtlinien * Arbeitskreis Umweltgesetzgebung * Arbeitskreis Design und Baugruppe * OrganisationUnternavigation öffnen ZurückNavigation schließen * Organisation* Geschäftsstelle

* Vorstand

* Beirat

* Mitglieder- und Dienstleisterverzeichnis * Linkliste COVID-19 * Aus- und WeiterbildungUnternavigation öffnen ZurückNavigation schließen * Aus- und Weiterbildung* Themenübersicht

* Zertifizierter Elektronik-DesignerUnternavigation öffnen ZurückNavigation schließen * Zertifizierter Elektronik-Designer * ZED Level I - Grundlagenkurs Leiterplattendesign * ZED Level II - Leiterplatten-Baugruppendesign 1 * ZED Level III - Leiterplatten-Baugruppendesign 2 * ZED Level IV - Design- und Technikseminare* Seminare

* IPC Schulungen

* Lötschulungen

* Inhouse Schulungen* Seminarkalender

* VeranstaltungenUnternavigation öffnen ZurückNavigation schließen * Veranstaltungen* FED-Konferenz

* Veranstaltungskalender* Regionalgruppen

* PCB-Designer-Tag

* PCB Design Award

* PublikationenUnternavigation öffnen ZurückNavigation schließen * Publikationen * Bibliothek des Wissens* FED kontakt

* Schulungsfilme

* IPC-DokumenteUnternavigation öffnen ZurückNavigation schließen * IPC-Dokumente* IPC DRM-FAQ

* FED-Shop

* Wissensdatenbank

* FED-Forum

* Aktuell

* Presse

* Newsletter

* Kontakt

* Login

* Stellenmarkt

* Youtube

* FED-Shop

* Suche

Fachverband für Design, Leiterplatten- & Elektronikfertigung Fachverband für Design, Leiterplatten- & ElektronikfertigungNavigation öffnen

* Verband

* Über uns

* Mitglied werden

* Regionalgruppen

* Arbeitskreise

* Organisation

* Mitglieder- und Dienstleisterverzeichnis * Linkliste COVID-19 * Aus- und Weiterbildung* Themenübersicht

* Zertifizierter Elektronik-Designer* Seminare

* IPC Schulungen

* Lötschulungen

* Inhouse Schulungen* Seminarkalender

* Veranstaltungen

* FED-Konferenz

* Veranstaltungskalender* Regionalgruppen

* PCB-Designer-Tag

* PCB Design Award

* Publikationen

* Bibliothek des Wissens* FED kontakt

* Schulungsfilme

* IPC-Dokumente

* FED-Shop

* Wissensdatenbank

* FED-Forum

* Aktuell

* Presse

* Newsletter

* Kontakt

* Login

* Stellenmarkt

* Youtube

* FED-Shop

* Suche

FED-Shop Mitglied werdenNewsletter

Der FED betrachtet es als Aufgabe und Verpflichtung, durch Angebote zur beruflichen Aus- und Weiterbildung, durch die Bereitstellung praxisnaher IPC-Richtlinien und durch die Förderung des Erfahrungsaustausches einen wesentlichen Beitrag zur Wettbewerbsfähigkeit der Elektronikbranche zu leisten.FED E.V.

Frankfurter Allee 73c10247 Berlin

Tel. +49 30 340 603050 Fax. +49 30 340 603061info@fed.de

* © 2020

* Impressum

* Datenschutz Webinare* Datenschutz

* AGB

* Sitemap

* Verband

* Über uns

* Mitglied werden

* Regionalgruppen

* Arbeitskreise

* Organisation

* Mitglieder- und Dienstleisterverzeichnis * Linkliste COVID-19 * Aus- und Weiterbildung* Themenübersicht

* Zertifizierter Elektronik-Designer* Seminare

* IPC Schulungen

* Lötschulungen

* Inhouse Schulungen* Seminarkalender

* Veranstaltungen

* FED-Konferenz

* Veranstaltungskalender* Regionalgruppen

* PCB-Designer-Tag

* PCB Design Award

* Publikationen

* Bibliothek des Wissens* FED kontakt

* Schulungsfilme

* IPC-Dokumente

* FED-Shop

* Wissensdatenbank

* Service

* FED-Forum

* Aktuell

* Presse

* Newsletter

* Kontakt

* Login

* Stellenmarkt

* Youtube

* FED-Shop

* Suche

Details

Copyright © 2024 ArchiveBay.com. All rights reserved. Terms of Use | Privacy Policy | DMCA | 2021 | Feedback | Advertising | RSS 2.0